2023 openDACS Open EDA and Chip Design Competition-Topic 1

赛题1:功能向量的时序电路故障模拟器

主办单位: 工业和信息化部、江苏省人民政府、湖南省人民政府

承办单位: 开放原子开源基金会、央视网、江苏省工业和信息化厅、无锡市人民政府、江苏软件产业人才发展基金会、苏州工业园区、无锡高新区等

联合承办单位: openDACS工作委员会、中国科学院计算技术研究所、中国科学院微电子研究所、北京大学、复旦大学、清华大学、北京开源芯片研究院、深圳微纳研究院、深圳华秋电子有限公司

本赛项聚焦: 集成电路产业的数字设计、模拟设计、芯片制造、芯片封装、处理器设计自动化、生成式芯片设计等领域,对促进产业高质量发展具有重要意义。

本赛项包含: 五个方向共计10道赛题。

出题单位: openDACS工委会SIG1 设计验证&测试综合

赛题Chair: 李华伟

1. 赛题背景

故障模拟(fault simulation)是芯片测试的重要步骤,是测试向量生成系统(ATPG)和故障诊断的重要组成部分,主要用于模拟故障电路的行为,评估测试向量对电路内部可能存在的故障的检测能力。简单来说,故障模拟就是通过比较无故障电路和故障电路在特定测试向量下的逻辑仿真结果,来确定被测故障能否被检测到。

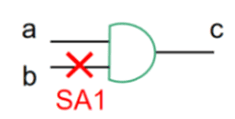

芯片在制造过程中,不可避免地会受到各种不可控因素的影响,导致制造出来的芯片存在各种缺陷。对于存在于芯片内部的缺陷,为了能够采用故障模拟等自动化方式检测缺陷,以及能够量化对缺陷的检测质量,通常会将缺陷抽象为各种故障模型,如固定型故障(stuck-at fault)、跳变延时故障(transition delay fault)、路径延时故障(path delay fault)等。其中,最为常用的故障模型是固定型故障。如图1所示,假设该与门的输入节点b存在stuck-at-1(缩写为SA1)故障,当我们同时对节点a、b施加激励(a=1,b=0)时,节点c的预期输出为“0”,但由于该故障的存在,节点c实际输出为“1”,也就代表着节点b处的SA1故障被测试向量(a=1,b=0)检测到了,这也就是故障模拟的一个简单流程。

功能向量属于测试向量的一种,它是在电路的功能运行条件下生成的一种向量,用于测试电路的内部状态,并检测电路可能存在的制造缺陷。与结构测试向量(也称扫描向量)不同的是,功能向量本质上是时序向量,在时间轴的不同时钟周期上有不同的向量输入值,且电路内部节点的逻辑状态依赖于前面时钟周期输入的仿真结果。这也就意味着,对于功能向量的故障模拟来说,无法采用常用于结构测试向量模拟的位并行方法。同时,功能向量可能涵盖数万甚至上百万个时钟周期的电路运行过程,这也导致了针对功能向量的故障模拟十分耗时。

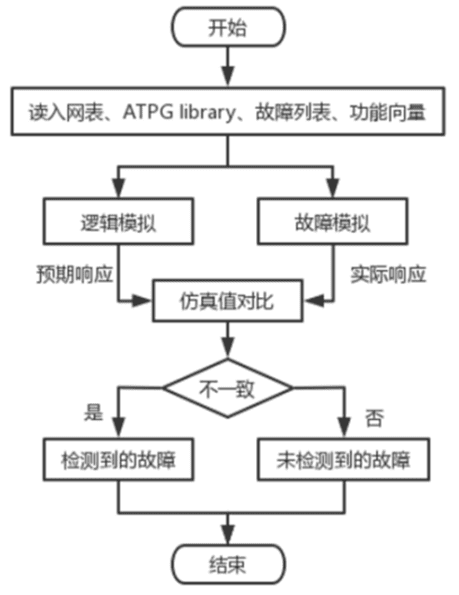

本赛题针对门级时序电路的单固定型故障,使用功能向量进行故障模拟,要求参赛队伍能够选取合适的算法,并尽可能采用并行模拟等性能优化方法,提供高性能的功能安全性评估。图2给出了功能向量的门级故障模拟简单流程示意图。

2. 赛题描述

2.1 描述

本赛题需要参赛队伍结合对功能向量和故障模拟的理解,设计一个C++程序,该程序应能读取赛题方提供的门级网表、ATPG library、故障列表和功能向量等文件,并通过对文件进行正确的解析和处理,完成对功能向量的故障模拟。程序输出为检测到的故障列表和未检测到的故障列表。

其中,参赛队伍需要完成以下几点:

(1)正确读入网表文件,并结合ATPG

library的信息,将标准单元网表转化为适合进行仿真的网表结构。

(2)正确读入故障列表文件,结合故障列表的信息,在网表中正确的位置插入对应的故障。

(3)正确读入功能向量文件,获取对应输入节点的激励,和输出节点的预期响应。

(4)进行无故障电路的逻辑模拟,获取电路内部节点在对应时钟节点的无故障仿真值。

(5)进行故障模拟,在对应时钟节点测量电路输出节点的实际响应,根据预期响应和实际响应的对比结果,确定故障是否能被当前的功能向量所检测到。

(6)根据故障模拟的结果,分别输出检测到的故障列表和未检测到的故障列表。

本赛题允许参赛队伍结合算法的具体需求,使用多线程进行并行加速。考虑到参赛队伍的开发硬件环境不一致,为了公平起见,本赛题限制最大使用的线程数量为4。

2.2 赛题Case

赛题共建方为参赛队伍提供赛题Case用于验证和优化设计的程序,下面是对所提供的文件的简单实例。

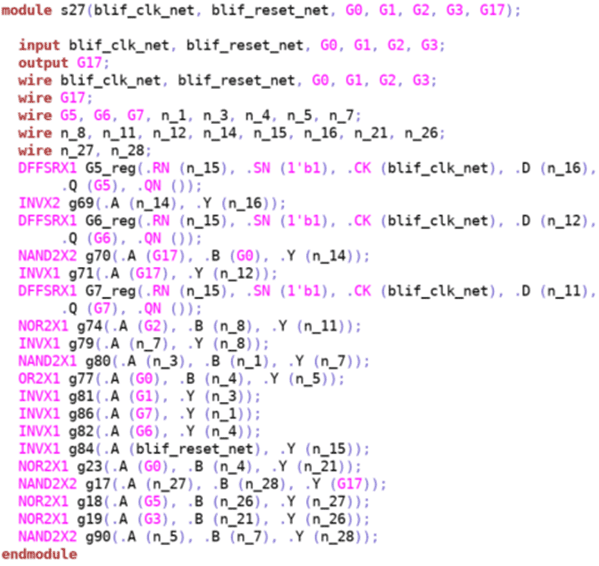

(1)Verilog平面化网表

平面化的网表由一个module构成,定义了电路的输入节点、输出节点和实例化的标准单元等信息。赛题共建方为参赛队伍提供了已开源的Verilog网表parser,供参赛队伍参考使用,同时也允许参赛队伍使用自己开发的parser。

图3给了一个例子。

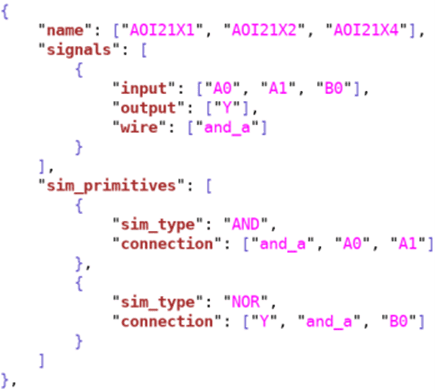

(2)ATPG library

本赛题提供的ATPG library采用JSON(JavaScript Object Notation)格式。JSON是一种简单的数据交换格式,已被证明很有用并足够简单。举例来说,通过如下的方式来表示一个AOI单元,其他单元也是采用相同的结构来表示。

图4给出了ATPG library的JSON描述示例,每个标准单元包含3个属性:name,signals和sim_primitives。

name:数组形式,包含多个相同逻辑功能但驱动能力不同的单元名;

signals:包含三种类型的信号,input,output和wire;

sim_primitives:一个或多个自定义单元,每个自定义单元包括两个属性,sim_type和connection,分别表示单元的类型和连接关系,在connection中第一个信号是输出,其余是输入。

(3)故障列表

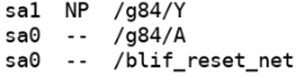

故障列表的格式十分简单,仅包含了故障类型(sa0或sa1)、故障检测状态(NP、DT、ND或--,其中NP表示not analyzed,DT表示detected,ND表示not detected,--表示当前故障与上述故障为等价故障。在输入故障列表中,所有故障均为NP状态)和故障位置(标准单元的实例化名字和对应引脚名字)。

图5给出了一个简单实例,其中包含三个故障,分别位于实例化的标准单元g84的Y引脚和A引脚,以及电路输入节点blif_reset_net,且这三个故障为等价故障。

(4)功能向量

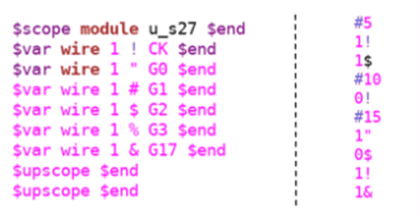

本赛题的功能向量采用VCD(Value

Change Dump)文件格式进行表示,VCD文件是标准波形文件,在数字电路模拟中用来记录指定电路节点信号值变化,记录了整个仿真的信息。需要说明的是,对于功能向量的故障模拟,如果测量信号仿真值的时钟节点不同,有可能会导致检测到的故障不同。 为了保证结果的一致性,要求参赛队伍统一按照以下方式检测故障: 在有电路输入节点的仿真值发生变化的时候,测量对比一次电路输出节点的仿真值,并以该对比结果判断故障是否被检测到。

如图6的例子是一个VCD文件的节选,需要分别在5ns、10ns、15ns处测量电路输出节点的仿真值并作对比。VCD文件的格式说明请直接参考其标准定义文件。

2.3 输出文件

本赛题要求参赛队伍的程序在完成故障模拟之后输出两份文件,一份存储检测到的故障列表,另一份存储未检出到的故障列表。输出文件的格式应与赛题共建方提供的赛题Case中故障列表的格式保持一致。

2.4 环境

建议参赛队伍的开发环境和运行环境,C++使用兼容C++20版本,并在Linux系统环境下进行开发。下述给出参考的软件环境。

• gcc 10.3.0

• g++ 10.3.0

• cmake 3.13.4

3. 评分标准

赛题共建方为本赛题准备了测试案例,将从测试案例中筛选并提供一部分案例给参赛队伍评估算法的质量;其余案例只作评分用途,不开放给参赛队伍。

测试评分:每个测试案例独立评分,遵循同样的评分标准。

(1)本赛题的故障检测结果以商用EDA工具的结果为golden结果,如果参赛队伍输出的结果与golden结果存在差异,则认为存在差异的故障检测失败。每出现一个存在差异的故障(等价故障按一个故障计算),则在计分基础上加0.01分。当存在差异的故障数量超过100个或超过总故障列表的1%时,则认为参赛队伍对当前案例的故障模拟失败,那么在该案例的评分为n(n为参赛队伍的数量)。

(2)案例通过条件(1)的情况下,假设参赛队伍有n支,则按程序总运行时间进行排序,第1名计1分,第2名计2分,以此类推,最后一名计n分。另外,对于单个测试案例的运行时间设置2小时的上限,超过2小时则结束程序的运行,并认为参赛队伍对当前案例的故障模拟失败,且在该案例的评分为n。

(3)案例通过条件(1)的情况下,如果存在运行时间相同的情况,则按分数相同,名次递增的规则评分。例如有2支队伍的运行时间相同且都是最快完成故障模拟的,则这2支队伍在评分上都是计1分,第3个队伍计3分。

对评分案例集中的每个案例进行评分后,总得分为单个案例得分的加权求和,其中单个案例的权重系数与该案例的规模成正相关。总计分越低的队伍,排名越高。

其他评分:设计文档质量,开源代码规范性等。

4. 参赛作品要求

4.1 初赛作品

参赛队伍提交该赛题的设计文档及作品源代码。

(1)设计文档要求是PDF文档,在文档中应写清楚技术实现细节并提供测试案例上的测试结果,包含以下几点:

• 功能描述

• 整体设计框架

• 功能模块细节设计

• 方案的优势和挑战

• 测试结果与数据分析

(2)作品源代码需要包含以下几项:

• 源代码

• 编译好的code二进制文件

• readme(对最终提交算法的基本说明,包括运行方式、输入格式说明等)

• 依赖的第三方库(如果有的话需要一并提供,防止由于版本不同而带来的结果差异)

4.2 决赛作品

参赛队伍在初赛作品的基础上,进一步完善作品,如提升关键算法的性能,优化代码的实现,增强代码可读性,符合开源代码规范性等,并提交最终源代码及设计文档参加决赛。

4.3 作品提交通道

参赛队伍提交作品前,需将队长在大赛官网上的注册邮箱、用户名、姓名、手机号码等信息邮件发送给本赛题工作人员(联系邮箱:Johnhw_2019@qq.com,邮件主题命名为:“队伍名称”建仓申请),工作人员将为该队伍在 AtomGit 上创建一个私有仓库,并将队长添加为该仓库管理员。参赛队伍完成作品后,将作品相关文档及源代码提交至该仓库即可。提交作品命名方式为:赛题名称+队伍名称+作品标题。AtomGit网址:https://atomgit.com/。

5. 奖励方案

(1)初赛评选冠军1名,奖励5万奖金;开源EDA新秀奖2名,奖励0.5万元;各颁发证书。

(2)初赛冠军将进入开源EDA与芯片赛项总决赛,在2024年4月进行总决赛路演,有机会获得“openDACS开源之星”及额外奖金2万元。

(3)为所有获奖队伍提供中国科学院计算所、开源芯片研究院、鹏城实验室、中科鉴芯(北京)科技有限责任公司等单位实习机会。

6. 参考文献

[1] L.-T. Wang , C.-W. Wu , and X.Wen. 2006. VLSI Test Principles and Architectures: Design for Testability (Systems on Silicon). Morgan Kaufmann Publishers Inc., San Francisco, CA, USA.

[2] H. Lee and D. Ha, "HOPE: an efficient parallel fault simulator for synchronous sequential circuits," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 15, no. 9, pp. 1048-1058, Sept. 1996.

[3] M. B. Amin and B. Vinnakota, "Data parallel fault simulation," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 7, no. 2, pp. 183-190, June 1999.

[4] S. Hadjitheophanous, S. N. Neophytou and M. K. Michael, "Scalable parallel fault simulation for shared-memory multiprocessor systems," 2016 IEEE 34th VLSI Test Symposium (VTS), Las Vegas, NV, USA, 2016, pp. 1-6.

[5] A. Bosio and G. D. Natale, "LIFTING: A Flexible Open-Source Fault Simulator," 2008 17th Asian Test Symposium (ATS), Hokkaido, Japan, 2008, pp. 35-40.

[6] W. K. Lam, Hardware Design Verification: Simulation and Formal Method-Based Approaches. Englewood Cliffs, NJ, USA: Prentice-Hall, 2008.

[7] L. Lai , Y. Yang , H. Li , X. Lin, Parallel Logic Simulation for Functional Test, Journal of Computer-Aided Design & Computer Graphics, 2023, 35(5): 803-810.

[8] TestMAX ATPG and TestMAX Diagnosis User Guide, Synopsys, Inc., Sunnyvale, California, USA, 2021.

[9] IEEE Standard Verilog Hardware Description Language, in IEEE Std 1364-2001, vol., no., pp.1-792, 28 Sept. 2001.

附1:10个赛题总体介绍

本赛项包含五个方向共计10道赛题,分别如下:

数字芯片EDA方向:

赛题1:功能向量的时序电路故障模拟器

赛题2:增量式时序优化算法

赛题3:FPGA工艺映射算法及优化

模拟芯片EDA方向:

赛题4:模拟电路优化算法

赛题5:运算放大器自动化设计

芯片制造EDA方向:

赛题6:基于BSIM-CMG模型的器件模型提参

处理器设计自动化EDA方向:

赛题7:ASIP基于OpenHarmony软总线特性的硬化IP设计

赛题8:基于开源PDK的硅基板互连设计

生成式芯片设计方向:

赛题9:基于自动芯片生成框架AutoChip(ChipGPT 2.0)的流水线CPU设计

赛题10:AutoChip(ChipGPT 2.0)芯片创意设计

附2:赛制/赛程

1. 竞赛流程

- 2023.09 -2023.11 在大赛官网、openDACS公众号、CCF集成电路设计专委公众号发布各个赛题

- 2023.09.30 - 2024.2.28 参赛队伍报名参赛,提交作品,并由出题方辅导改进

- 2023.10.15 在CCFDAC2023大会开源EDA专题论坛现场进行赛题答疑

- 2023.10.15 - 2023.12.30 在指定单位安排讲座(中科院、北大、复旦、清华、武汉理工、深圳技术大学等);在电子发烧友网站安排1-2次在线讲座

- 2024.03.31 初赛评审,评选各个赛题冠军及新秀奖,出题方辅导冠军队伍改进

- 2024.04.01 - 2024.04.15 决赛作品提交

- 2024.04 决赛评审,十个赛题冠军汇总评选出3名openDACS开源之星奖

- 2024.06(暂定) 开放原子开发者大会,公布获奖名单与线下颁奖

2. 竞赛咨询

请参赛队伍加入本赛项微信交流群“openDACS开源EDA与芯片大赛”,微信群二维码:

如微信群二维码过期,可直接联系本赛项负责人微信:WinPolestar,申请加入交流群。

参赛队伍在报名及提交作品后,可将报名信息、参赛作品发至

Johnhw_2019@qq.com。

3. 参赛队伍须知

本赛项正式开始比赛的要求为:报名队伍数量至少达到10支,且提交作品数量至少达到5个。若未达到报名队伍或提交作品的数量要求,则本赛项可能被延期或暂停,届时将由本赛项各共建方(中科院计算技术研究所、中国科学院微电子研究所、北京大学、复旦大学、清华大学、北京开源芯片研究院、深圳微纳研究院、深圳华秋电子有限公司)向您发出书面通知。

附3:作品提交要求

1. 参赛作品内容要求

各赛题具体作品内容要求详见“赛题”栏目中各赛题描述。

2. 参赛作品规范要求

(1)参赛作品须符合本届大赛赛项要求及主题,作品名称应能体现作品主要特征。

(2)参赛作品必须为原创作品,不可侵犯任何他人的专利权、著作权、商标权及其他知识产权,且不得违反国家相关法律法规。

(3)作品必须可分离原开发环境,具备可演示的运行环境,能够在组委会提供的测试账户上编译/运行或自行提供编译/运行环境。

(4) 作品允许使用他人开源代码,但必须在保持原有版权的基础上,注明出处和其它开源代码的依赖关系。提交作品时,必须在分析设计文档中明确说明作品中其他开源代码的作用及所占比例。

(5)作品应能正确运行并可达到预期结果。作品应与设计文档描述的功能一致,如未能实现设计文档中描述的所有功能,应注明未实现功能及其所占比例和重要程度。

3. 参赛作品提交要求

(1)参赛队伍提交作品前,需将队长在大赛官网上的注册邮箱、用户名、姓名、手机号码等信息邮件发送给本赛题工作人员(联系邮箱:Johnhw_2019@qq.com,邮件主题命名为:“队伍名称”建仓申请),工作人员将为该队伍在 AtomGit 上创建一个私有仓库,并将队长添加为该仓库管理员。参赛队伍完成作品后,将作品相关文档及源代码提交至该仓库即可。提交作品命名方式为:赛题名称+队伍名称+作品标题。AtomGit网址:https://atomgit.com/。

(2)参赛队伍均可在不改变作品名称和主要功能的基础上,持续推进作品迭代升级,对应赛程最后一次提交的作品为参赛作品。

(3)评审期间,参赛队伍须按照组委会的要求补充提交作品相关材料。

(4)所有已提交的参赛作品和相关材料原则上不予退还。

附4:评审规则与评审专家组

1. 评审规则

(1)各赛题评审细则详见"赛题"栏目中,每道赛题的验收标准。

(2)完成参赛作品文档说明,文档技术路径可行,并被方向专家评审后通过。

(3)代码功能完成指标要求,并提交规范的代码和详实的文档,最后经过评审代码合入到对应仓库。

(4)根据每道赛题中验收标准说明获得对应奖项。

2. 评审专家组

李华伟(组长,openDACS工委会主任兼SIG1负责人,中国科学院计算技术研究所研究员,处理器芯片全国重点实验室副主任,负责赛题1)

何均宏(联合组长,openDACS工委会联合主任兼执行总监,负责本赛题赛事组织运作,参与赛题7-10评选)

李兴权(鹏城实验室副研究员。负责赛题2)

罗国杰(openDACS工委会SIG2负责人,北京大学信息科学技术学院长聘副教授、高能效计算与应用中心执行主任。负责赛题3)

杨 帆(openDACS工委会SIG3负责人,复旦大学微电子学院教授,博士生导师。参与赛题2评选)

解壁伟(openDACS工委会SIG4负责人,中国科学院计算技术研究所和鹏城实验室助理研究员,参与和负责“一生一芯”和开源EDA等项目。参与赛题2\3评选)

叶佐昌(openDACS工委会SIG7负责人,清华大学集成电路学院副研究员,负责赛题4、5)

李志强(openDACS工委会SIG5负责人,中国科学院微电子研究所研究员,EDA中心负责人,负责赛题6)

刘永新(深圳市微纳集成电路与系统应用研究院助理院长,负责赛题7)

王郁杰(之江实验室,研究专家,负责Chiplet等分离制设计方法的计算核设计、互连系统设计、EDA设计等工作,负责赛题8)

樊嘉祺(华进半导体,封装设计经理,负责2.5D/3D集成封装、晶圆级扇出封装、三维异质集成等封装设计、仿真技术研究。负责赛题8)

王 颖(openDACS工委会SIG8负责人,中国科学院计算技术研究所研究员,负责赛题9-10)

黄 宇(华为半导体科学家,深圳海思EDA首席架构师和EDA实验室主任。参与赛题1/4/8评选)

杨 凡(深圳国微芯科技有限公司研发副总裁,参与赛题2评选)

刘 勇(深圳华秋电子有限公司旗下电子发烧友平台社区运营负责人,负责线上讲座,参与赛题7-10评选)