iEDA-Chip-005

小于 1 分钟

芯片参数

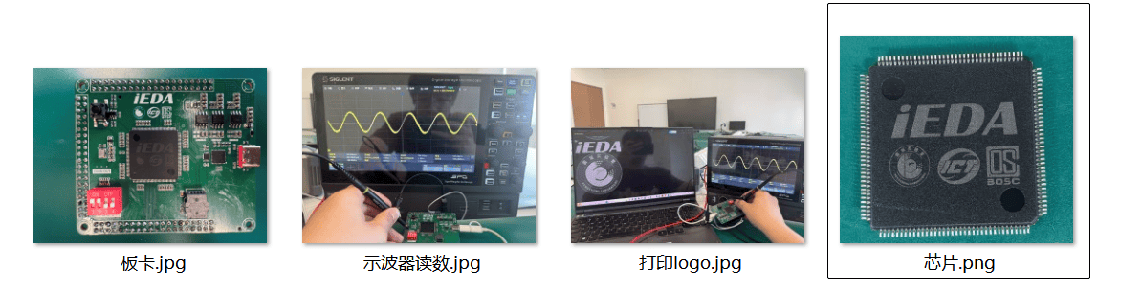

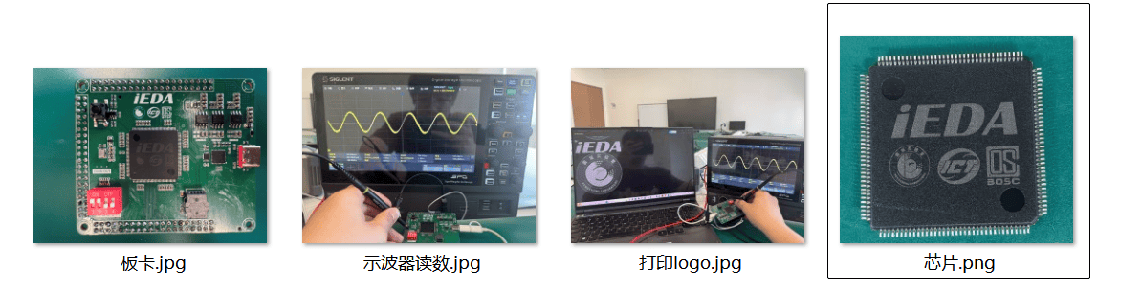

第5次:20250105,在28nm工艺处理器芯片“果壳”(含321个宏模块,82.9万标准单元,1049万门晶体管,TT: 900MHz,4.0mm*2.7mm),测试频率1000MHz

SoC规格:

- 一个11级顺序单发射RV64I MAC处理器核

- 实现AXI4总线互联网络,集成一个PLL,设计有三个时钟域

- 集成了UART、QSPI Flash、ChipLink、SDRAM、VGA、PS/2外设

版图结果

芯片参数

第5次:20250105,在28nm工艺处理器芯片“果壳”(含321个宏模块,82.9万标准单元,1049万门晶体管,TT: 900MHz,4.0mm*2.7mm),测试频率1000MHz

SoC规格:

版图结果