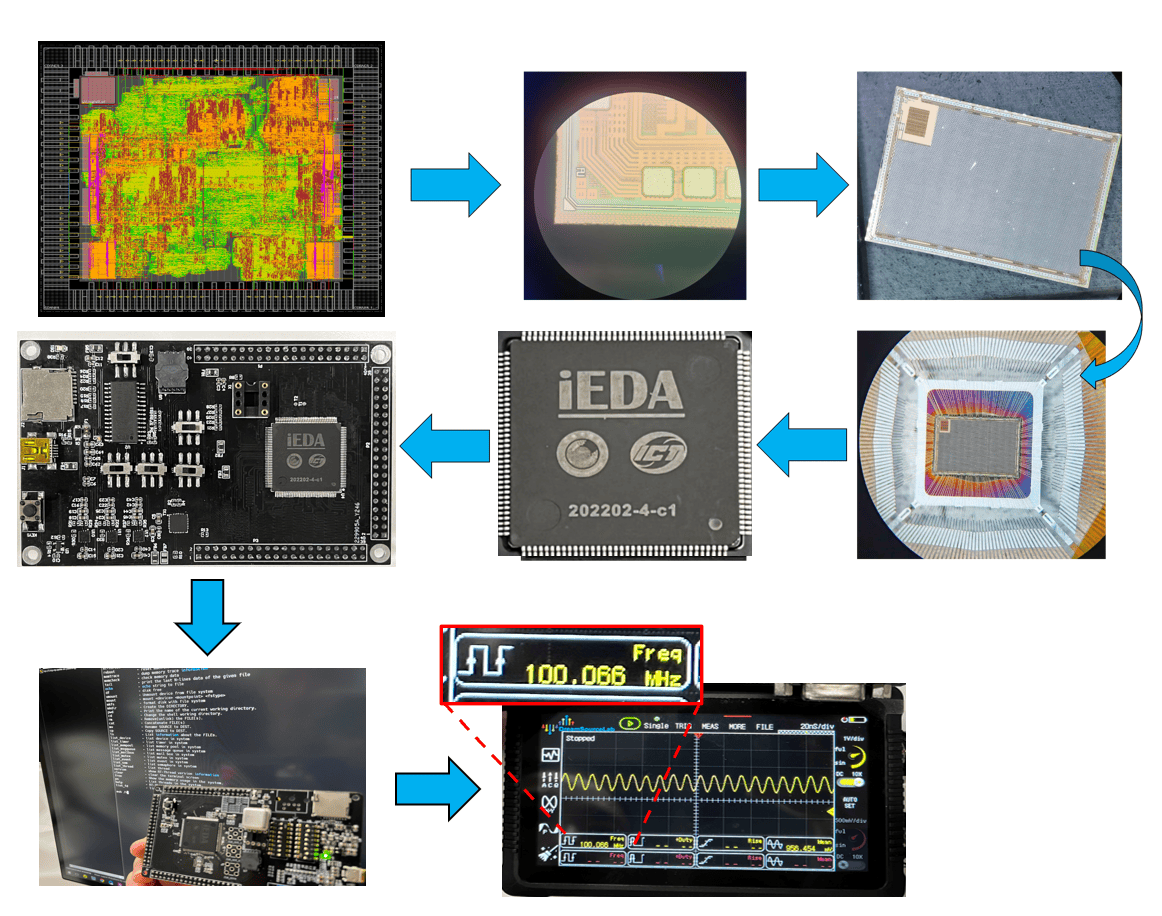

Tape-out

Less than 1 minute

(Introducing the chips designed based on iEDA)

Tape-out Plan in 2024

In April 2024, using the "YSYX" sixth phase or "Nanhu-G" design, a 28nm process, 5 million gate-level processor chip is expected to achieve a clock frequency of 400 MHz.

Highlights: Compared to previous tape-outs, the tools of this tape-out plan have the following improvements: Using iSTA to assist in the timing estimation of front-end RTL code development, supporting intelligent placement tools for macro cells, supporting timing-driven placement tools, and conducting tape-out design with the help of AiEDA.