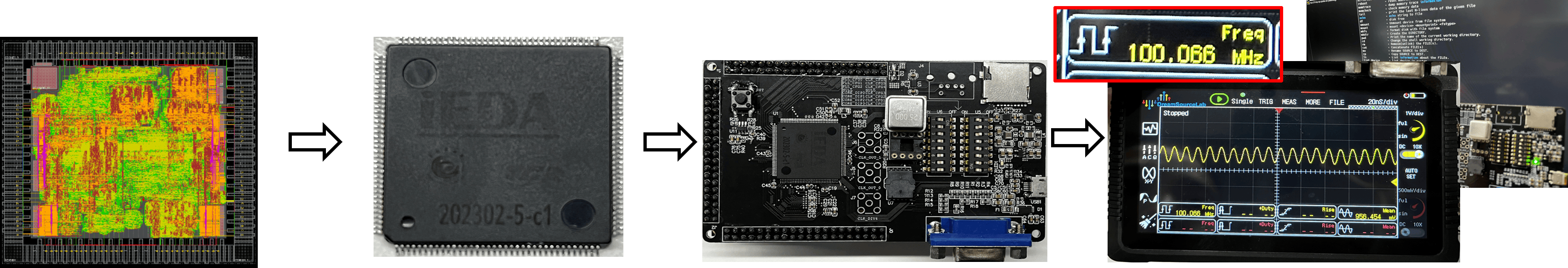

iEDA-Chip-003

Less than 1 minute

Chip Parameters

Second Tapeout: 20220812, 1.5M-gate-level processor chip designed in the "One Chip for a Lifetime" 28nm technology, third phase, achieved a 200MHz tapeout result;

SoC Specifications:

- A 11-stage, single-issue RV64I MAC processor core

- AXI4 bus interconnect network, with an integrated PLL, designed with three clock domains

- Integrated UART, QSPI Flash, ChipLink, SDRAM, VGA, PS/2 peripherals

Chip Parameters:

•Technology: 28nm

•Area: Approximately 1.5 × 1.5 cm

•Power Consumption: Dynamic = 317mW, Leakage = 29 mW

•Frequency: 200MHz

•Scale: 1.5M Gates

•Features: 11-stage pipeline with cache, IPs: UART, VGA, PS/2, SPI, SDRAM, two PLL modules output clocks, supports Linux

Layout Results