5.1 标准单元

作为ASIC(特定应用集成电路)设计中的基本构建单元,标准单元具有明确定义和预特性化的特点。它们具备高度的可重用性,能够在不同的项目或系统中被重复使用,从而节省大量ASIC设计时间。可重用性的概念意味着设计中的某个组件、模块或部分可以在多个不同的场景中灵活重复使用,避免了重复设计的工作量和时间。

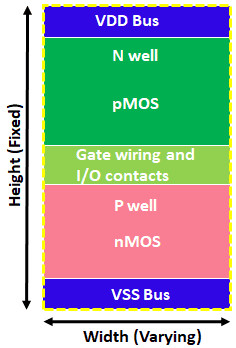

标准单元布局

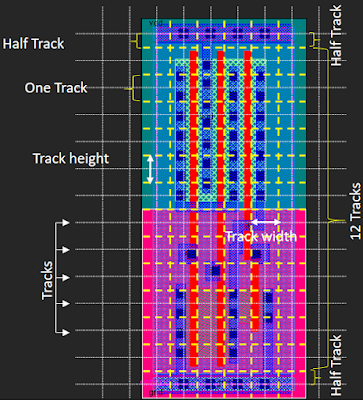

所有标准单元的高度相等,宽度各不相同。标准单元的主要特征在下图中进行了解释。

图1 标准单元布局样式

在标准单元的布局中,顶部有VDD电源线,底部有VSS电源线,它们都绘制在金属1层上。在VDD电源线和VSS电源线之间,有三个关键区域,分别是n型井区、n型井和p型井之间的间隙,以及p型井区。n型井区靠近VDD电源线,而p型井区则靠近VSS电源线。pMOS晶体管构建在n型井内,因此所有的pMOS晶体管都位于单元的上半部分,同样地,所有的nMOS晶体管都位于标准单元的下半部分。

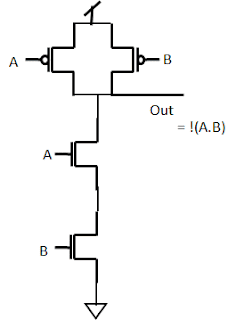

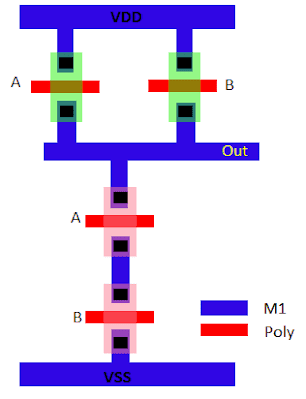

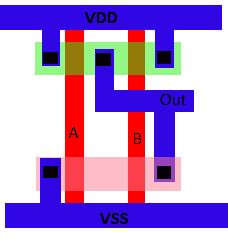

标准单元的原理图布局可以以多种不同的方式绘制。以NAND门为例,可以以两种不同的样式来设计布局。一种布局样式是将两个nMOS晶体管堆叠在一起,不处于同一水平上。另一种布局样式则将所有的nMOS晶体管以及pMOS晶体管分别绘制在一个水平上。此外,布局样式中的门可以是水平绘制的,或者nMOS和pMOS可以分别绘制。

图2 NAND门的原理图

图3 NAND门的布局

图4 NAND门的布局

图2显示了NAND门的原理图,图3和图4显示了图中原理图的两种不同布局。在图3中,两个nMOS不处于同一水平上,它们被堆叠在一起,但在图4的布局中,所有nMOS都位于一个水平上,所有pMOS都位于一个水平上。而且在图3中,门是水平绘制的,而在nMOS和pMOS中不共享。但是在图4中,所有多晶硅栅极是垂直绘制的,同时对nMOS和pMOS都是共用的。

为什么要选择像第二种布局样式那样的设计呢?原因有很多,下面是其中一些:

- 节省设计面积:所有标准单元的n型井和p型井都位于同一水平,它们可以方便地相邻并形成一个共享井,从而节约了大量的面积。

- 便于自动布置:所有标准单元具有相同的高度,可以轻松地放置在标准单元行中,因此自动布局工具能够更容易地完成这项工作。所有标准单元的电源线也位于相同的位置上,使得电源线的布局变得更加简单。

- 易于布线:标准单元的引脚位于水平和垂直轨道的交叉点上,这使得自动布线工具能够轻松地进行布线。

标准单元中的轨道

标准单元中还存在轨道的概念,可以定义为绘制在金属层上的线。每个轨道代表着一个M1间距。标准单元的高度通常用轨道数量来衡量。举个例子,一个6T的标准单元意味着该单元的高度为6个M1轨道。这里展示了一个示例,它是一个13T高度的标准单元。

图5 一个13T高度的标准单元

在这个例子中,一个轨道的高度为190纳米。因此,单元的总高度为13T = 2470纳米(13 x 190),宽度为5T = 950纳米(5 x 190)。

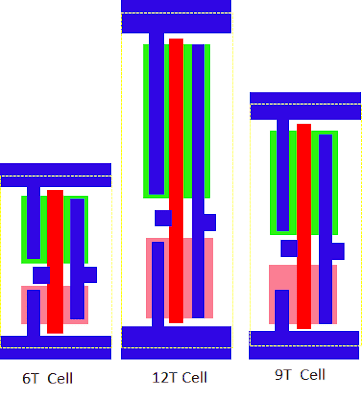

对于标准单元库,通常会提供各种不同轨道高度的选项。根据ASIC的需求,可以选择相应轨道高度的标准库。通常有三个标准单元库集合,分别是小型晶体管标准单元、大型晶体管标准单元和中型晶体管标准单元。下面是一些示例,展示了不同高度的标准单元,分别为6T、12T和9T。

图6 不同高度的标准单元

小型晶体管标准单元(6T)适用于高密度设计,具有较低的功耗。它们在移动应用和超低功耗应用中非常受欢迎,也广泛用于嵌入式微控制器。

大型晶体管标准单元(12T)占用面积较大,但具有出色的性能和速度。它们用于高速计算和关键块等场景,能够提供卓越的性能。

中型晶体管标准单元(9T)在大型晶体管和小型晶体管之间取得了平衡,既能满足面积要求,也能保持性能。它们被广泛应用于通用计算、GPU和通用电路等领域。

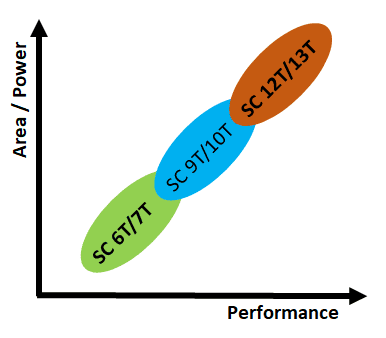

在实际设计中,我们需要根据需要选择不同高度的标准单元,权衡面积/功耗和性能之间的关系。为了更好地选择,我们可以比较它们的性能和面积,进一步确定最适合特定应用的标准单元。

图7 各种高度标准单元的性能和面积权衡

这些单元的各种应用如下:

- 小型晶体管单元(6T单元)

- 最小面积和低功耗

- 移动应用

- 超低功耗应用

- 嵌入式微控制器

- 大型晶体管单元(12T单元)

- 占用面积大

- 高性能和速度

- 高速计算

- 关键块

- 中型晶体管单元(9T单元)

- 面积和性能之间的平衡

- 通用计算

- GPU

- 通用电路

总之,物理设计中的标准单元是ASIC设计的基本构建单元,具有高度的可重用性。通过合理布局和使用不同高度的标准单元,我们能够实现高效、灵活地进行芯片设计,满足各种应用的需求。

参考资料

https://teamvlsi.com/2020/05/standard-cells-in-asic-design-standard-cells-in-vlsi.html