5.8 连接单元

在当今高科技领域,物理设计中的连接单元扮演着不可或缺的角色。它们是用于连接逻辑门输入端的标准单元,能够提供稳定的高电平或低电平信号。由于晶体管的一些限制,尤其是在较低技术节点上,高低电平信号不能直接应用于任何晶体管的门。因此,在本文中,我将向您介绍连接单元的必要性、原理图、功能和布局。

连接单元的必要性:

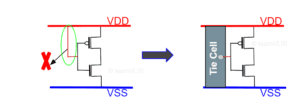

在较低技术节点中,多晶硅门下的栅氧化物非常薄且是晶体管最敏感的部分。在制造过程中(相关问题是天线效应)以及在操作过程中,我们需要特别注意这种薄的栅氧化物。已经观察到,如果多晶硅门直接连接到VDD或VSS以提供恒定的高/低输入信号,并且如果供电电压出现任何浪涌/毛刺,会导致敏感栅氧化物受损。为避免上述损坏,我们避免直接将VDD或VSS连接到任何逻辑门的输入。连接单元用于将任何逻辑的输入连接到VDD或VSS。

图1 连接单元的必要性

连接单元有两种类型:

- 连接高电平单元:输出始终为高电平。

- 连接低电平单元:输出始终为低电平。

连接单元的原理图:

连接单元的设计基于电子电路的原理图,下面将介绍连接单元常见的原理图元素和设计要点。

- 信号线和引脚

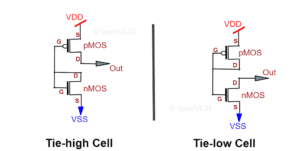

连接单元的原理图中,信号线负责传输信号,而引脚则是连接单元和其他元件之间的物理接口。通过信号线和引脚的合理设计,可以确保信号在连接单元和其他元件之间自由流动。连接单元没有输入引脚,只有一个输出引脚。连接高电平单元的输出始终为高电平,连接低电平单元的输出始终为低电平,它是无毛刺的输出,连接到任何逻辑门的输入。连接高电平单元和连接低电平单元的原理图如图2所示。

图2 连接高电平和连接低电平单元

在连接高电平单元中,nMOS的漏极和栅极短接在一起,并连接到pMOS的栅极,输出来自pMOS的漏极。而在连接低电平单元中,pMOS的漏极和栅极短接在一起,并连接到nMOS的栅极,输出来自nMOS的漏极。

缓冲器和驱动器

为了增强信号传输的可靠性和稳定性,连接单元的原理图中通常包含缓冲器和驱动器。缓冲器可以增强信号的驱动能力和传输速度,而驱动器则负责适配不同输入和输出的电平和电流。路由器和交换机

对于复杂的连接单元设计,路由器和交换机作为原理图中的重要元素,用于实现不同信号路径的选择和切换。它们能够灵活地连接不同的元件,提供更为复杂和灵活的信号路由功能。

连接单元的功能:

连接高电平和连接低电平单元的工作原理相似。这里解释了连接高电平单元的工作原理。可以类似地思考连接低电平单元。从图2连接高电平单元,nMOS的漏极和栅极短接。

所以Vg = Vd

==> Vgs = Vds

因此,Vds > Vgs -Vt

这表明nMOS将始终处于饱和区。漏极和栅极短接的MOS配置通常称为二极管连接的晶体管。当在此处nMOS表现为二极管时,pMOS的栅极始终为低电平,因此pMOS始终处于导通状态。当pMOS处于导通状态时,其漏极(输出)将始终为高电平。

类似地,对于连接低电平单元,pMOS始终处于饱和区,因此nMOS的栅极始终为高电平,因此nMOS的漏极将始终处于低逻辑电平。

这里还有一点很重要,即VDD或VSS的突然波动不会传播到连接单元的输出。

连接单元的布局:

连接单元的布局是物理设计过程中关键的一环,直接影响到电路的性能和制造效率。下面将介绍几个常见的布局原则和策略。

紧凑布局:指将连接单元尽可能地紧密排列,减小信号传输的距离和延迟。通过紧凑布局,可以提高电路的速度和效率,并减少空间占用,提高集成电路的密度和制造效率。

信号分组和层次化:布局时,可以根据信号的类型和传输特点进行分组,将经常通信的元件和信号线放置在相邻的位置。同时,通过层次化布局,可以将关联的电路模块放置在不同的层次,提高电路的可维护性和布线的灵活性。

电源和地线布局:连接单元中合理的电源和地线布局对于电路的可靠性和抗干扰性至关重要。通过将电源和地线靠近相关的元件和信号线,可以减小电源和地线的阻抗,并降低电路的干扰和噪声。

仲裁和调度电路布局:对于大规模的连接单元设计,需要合理布局仲裁和调度电路以实现并行处理和资源共享。通过将仲裁和调度电路放置在靠近需要连接的元件附近,可以提高电路的灵活性和效率。

谢谢

[1] https://teamvlsi.com/2021/08/tie-cells-in-physical-design.html