1.2 VLSI 设计流程

在这篇文章中,将要展示 VLSI 设计流程。VLSI 流程的第一步是设计规范,这个规范通常来自于客户端,客户会写下他们想要在芯片中开发的功能和所需的规格。接下来,整个设计过程将经历不同的设计周期,通常需要6到24个月才能完成设计,具体取决于芯片内部的复杂性。从产生制作芯片的想法到获得芯片实物,主要分成三个部分:前端设计、后端设计、制造。

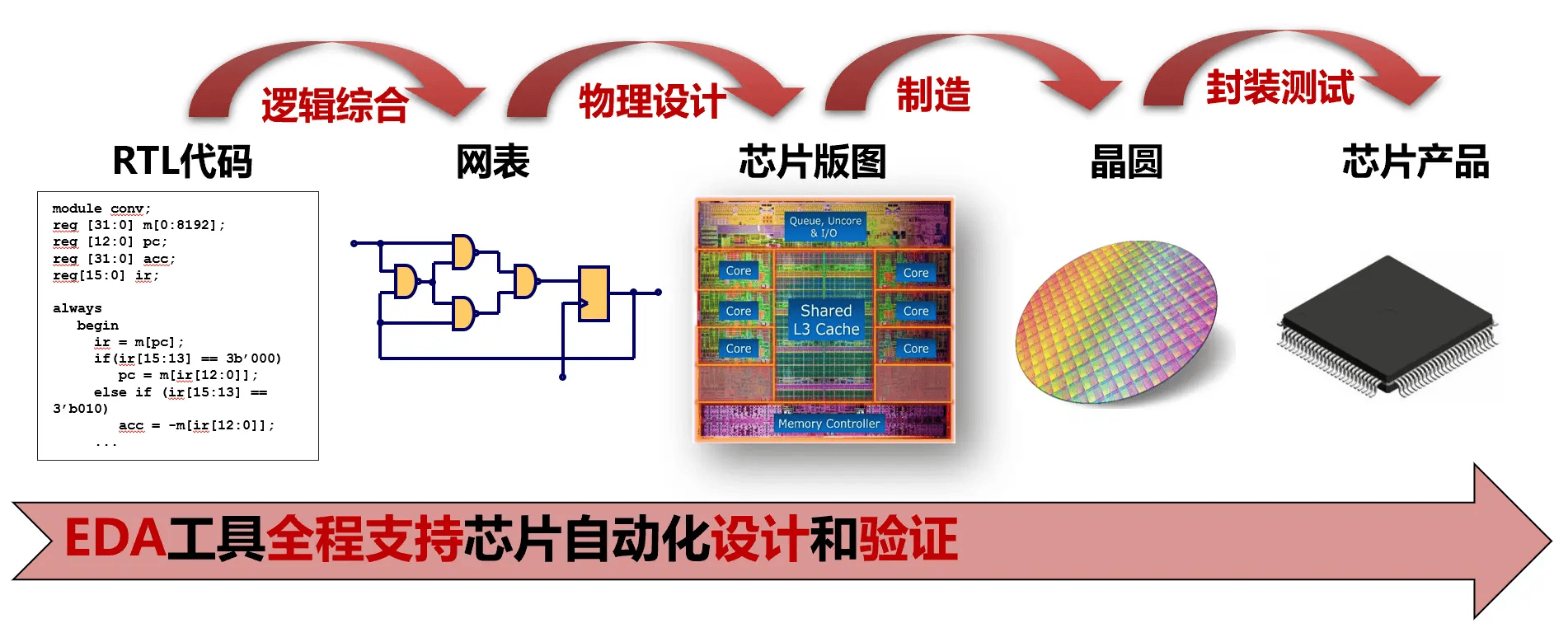

图1 芯片设计与制作流程

在集成电路设计中,从 Verilog/VHDL 代码(RTL 级)编写验证再通过综合(synthesis)转换成门级网表(gate netlist)的过程称为数字前端设计。接下来的工作就是门级网表的物理实现,即把门级网表转换成版图,这个过程通常称为后端设计(backend design)。版图通过代工厂制造并封装形成芯片产品的过程,成为制造。

1 VLSI 设计流程概述

(1)前端设计

前端设计过程从客户端收到的规范开始。首先,RTL设计工程师通常使用 HDL [Hardware Description Language : 硬件描述语言],如Verilog或VHDL将规范转换为RTL代码。这些RTL代码描述了芯片的逻辑功能和数据流。

一旦RTL代码编写完成,RTL设计人员会使用RTL模拟器对代码进行功能验证。在模拟器中,设计人员可以模拟各种输入情况,并检查设计的功能是否正常。如果没有发现错误,并且功能验证工程师对代码进行了验证,那么RTL代码就可以进入下一个阶段,这个过程也成为前仿真。

大体流程如下:

规格制定:根据产品需求,制定相应的规格;

架构设计:根据规格需求,设计芯片架构,系统功能模块划分,定义BUS结构,系统模型,制造封装和板卡要求,输出设计文档;

功能实现和验证:按照每个功能模块,实现相应的RTL代码并进行功能仿真验证,期间主要借助Debug工具和波形仿真工具,输出RTL级的Verilog代码。如有需要,每个IP功能模块需进行SoC集成,功能验证。对于验证,可以借助FPGA或者硬仿来完成;

逻辑综合:对RTL代码进行逻辑编译形成状态机或真值表,接着进行逻辑优化设计形成GTech电路,然后通过工艺库映射得到网表,并进行电路级仿真和形式化验证,输出Netlist级的Verilog代码。综合后进行DFT,插入一些测试模块;

(2)后端设计

后端设计是指从门级网表开始到芯片版图完成的设计过程,包括了逻辑综合、物理综合、时序分析、时序优化、DRC与LVS验证、设计规则填充、后仿真等步骤。完整的后端设计由后端半定制与后端全定制两个设计部分组成:

后端全定制设计是指在设计初期最先按照设计需求设计出的物理单元库,物理单元库由标准单元库、IP 库及满足特殊需求的定制部件单元等组成。该物理库为后续后端半定制设计提供物理实现基础。

后端半定制设计是指使用布局布线工具并基于后端全定制阶段完成的标准单元库及 IP 库并根据前端设计完成整个芯片的组装与实现,这个过程又称为数字后端设计(自动布局布线-APR)。常用工具有 IC Compiler、PrimeTime、PrimeRail 等。

后端半定制设计由于在设计中占主要部分的 标准单元库(standard cell library) 里各个单元的高度相等,宽度不限,单元中的电源、地线及输入输出端口位置都有特殊的规定,使得单元与单元连接时变得简单、有条理,布局也有规律,简化了设计过程。当然,使用标准单元进行设计存在一些问题:可用元件有限、难以高效构造复杂器件(例如乘法器)。

后端全定制流程如下:

- 单元库设计:从Foundary获得工艺库基本会含有IO,Memory和部分IP,以及PDK和单元库。但是对于单元库可以进一步优化设计,首先设计单元模型,进行单元电路版图设计,对单元进行参数提取,进行物理验证;

后端半定制流程如下:

布图规划:决定电路或者模块的形状和布置,以及端口、宏模块的位置;

电源规划:确定电源(VDD)和地(GND)的位置;

布局:确定不同模块中所有单元的空间位置;

时钟综合:确定时钟信号的缓冲、门控和布线,以满足规定的偏移和延迟;

总体布线:分配布线资源用于连接详细布线、分配布线到指定的金属层;

签核分析:在逻辑综合和物理设计过程中,需对电路和版图进行参数提取,时序,功耗,IR drop,电源和信号完整性等分析,确保获得的电路和版图是满足设计规格约束的;

物理验证:得到GDS版图之后,除了需要进行签核分析,还需进行物理结构上的验证,主要包括:设计规则检查(DRC),电学规则检查(ERC),版图和原理图比较(LVS)等。之后还需进行一次最后的仿真,以确保整个版图功能的正确性;

其中,步骤6-10统称为物理设计。对于综合获得的网表,需要设计布图,布局,时钟树综合,布线,ECO等步骤,最后得到GDS版图文件。当然,为了实现预期的PPA指标和满足设计规则,物理设计往往需要迭代多次。另外,物理设计的每个步骤也需要进行形式化验证以确认功能的正确性。

(3)制造

芯片制造是将芯片版图转化为芯片实体的过程,包括了掩模制作、晶圆制造、芯片封装和测试等步骤。制造过程中会涉及到多种技术,比如光刻、离子注入、蚀刻等,以及各种测量和测试手段,如显微镜、扫描电子显微镜、测试芯片等。

版图处理:在完成物理验证之后,芯片设计环节基本完成,接下来需要将版图交给Foundary来开掩膜(Mask)。需要对GDS版图进一步优化,进行OPC和RET,目的是为了增强分别率,减少生产变形错误,接着用于制作生成Mask;

制造封装测试:主要有Foudary和封测厂完成,回片;

PCB:在完成上述步骤后,基本可以得到一颗芯片,可以将其集成到需要的PCB进行实践验证和使用,PCB级板卡也设计到如何布局布线等问题;

2 后端设计部分详解

从前端工程师那里收到的 RTL 代码与后端设计技术无关,现在下一步是 逻辑综合 [Logic Synthesis]。

(1)逻辑综合

在逻辑综合中,设计的高级描述(RTL 代码)被转换为给定标准单元库和某些设计约束的优化门级表示。现在,代码采用特定标准单元库的门级网表的形式。在此阶段必须进行 LEC [Logic Equivalence Check : 逻辑一致性检查],以确保在综合过程中不会发生逻辑变化。在逻辑综合期间,我们还会得到有关时序功率和设计面积的各种报告。在此阶段,我们还将获得一个 SDC [Synopsys Design Constraint:Synopsys设计约束] 文件,该文件将在下一阶段使用。DFT [Design For Testability : 可测试性设计] 插入测试逻辑也在此阶段完成,以在制造完成后验证芯片。

(2)布局与布线

DFT 插入后的门级网表和 SDC 文件作为 PnR [Place and Route : 布局与布线] 的输入,并基于标准单元库,开始 PnR。PnR 阶段的目标是以最小的面积和最小的延迟放置所有标准单元、宏单元和 I/O 焊盘,并以没有 DRC [Design Rule Check : 设计规则检查] 错误的方式将它们布线在一起。该阶段的最终输出是GDSII文件形式的设计版图,这是业界版图文件的事实标准。

PnR阶段是一个非常具有挑战性的阶段,设计周期时间长,具体取决于芯片的复杂性。这个阶段进一步分为各个子阶段。主要阶段从 设计导入 [Design Import]开始,然后是 布图规划 [Floor Plan]、电源规划 [Power Plan]、布局 [Placement]、CTS [Clock Tree Synthesis : 时钟树综合] 和 布线 [Routing]。

在布线之后,我们预计设计已经满足了时序和所有DRC,但是在现代芯片中,在这个阶段关闭设计并不容易。因此,我们进一步进入 签核 [signoff] 阶段。

(3)签核

如果后端布局设计中存在一些时序违例,我们会进行进一步的 ECO [Engineering Change Order : 工程变更] 阶段,以解决这些时序违例。除了时序违例,还可能存在诸如 电压下降 [IR Drop]、DRC [Design Rule Check : 设计规则检查] 违例等问题,所有这些问题都会在此阶段得到解决,并以GDSII格式输出最终的不含任何违例的版图文件。这个过程在ASIC流程中被称为 流片 [tapeout]。这是最终的设计阶段,而GDSII文件则被发送到制造实验室用于芯片的制造。

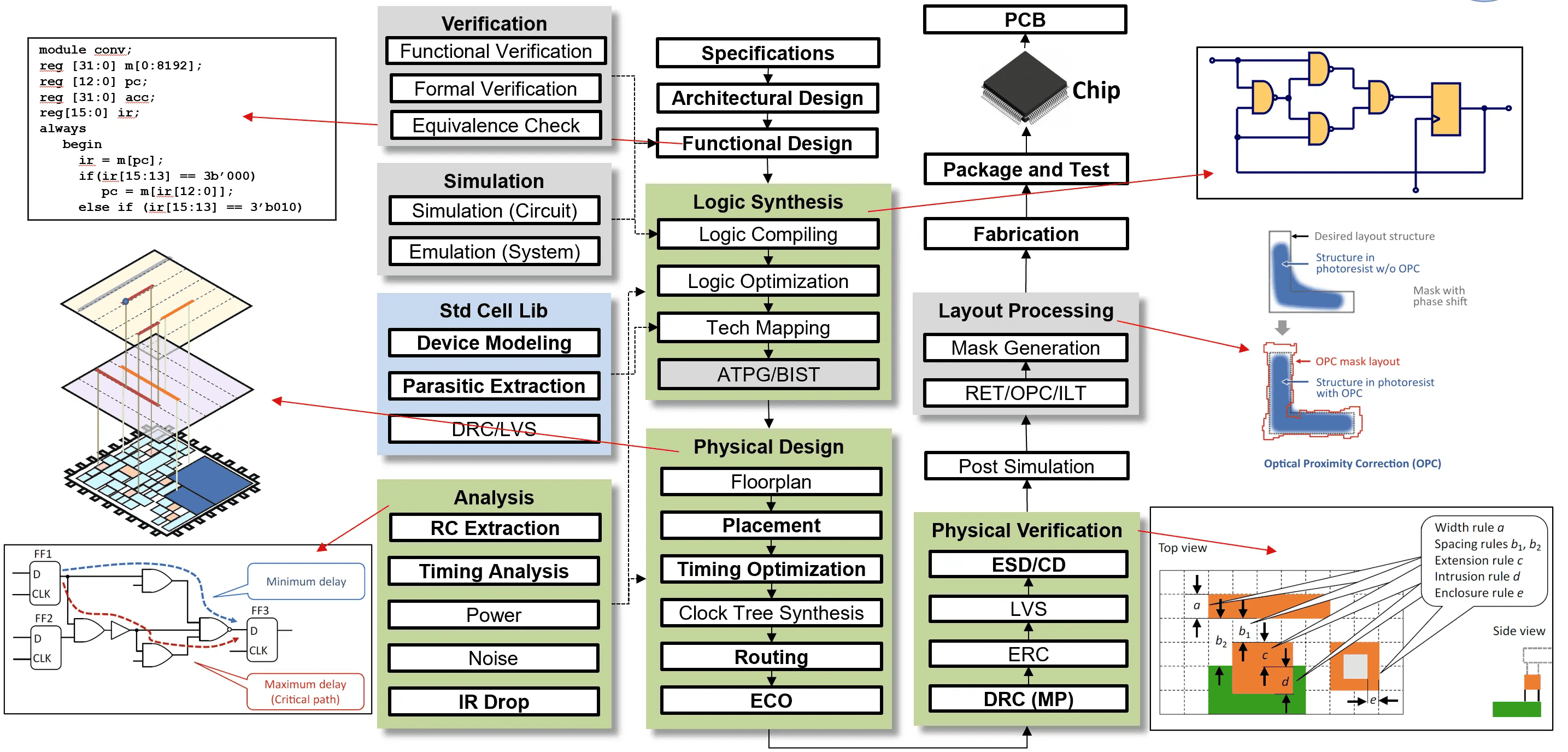

3 EDA工具涉及的领域

整个芯片设计过程中,主要产生的EDA工具涵盖的分类和内容可以总结为以下的五大方面,

- 设计综合: 设计环节主要包括,高层次综合,逻辑综合,物理设计,封装设计,PCB设计

- 仿真模拟: 仿真环节主要包括:TCAD,晶体管仿真,逻辑仿真,硬件仿真,场求解器

- 验证测试: 验证测试环节主要包括:功能验证,形式化验证,等效性检查,ATPG,BIST,物理验证

- 分析检查: 分析环节主要包括:跨时钟域,寄生提取,(静态)时序分析,功耗分析,温度分析,电压降分析,信号/电源完整性分析

- 掩膜准备: 掩膜环节主要包括:版图分解,OPC,RET,掩膜生成

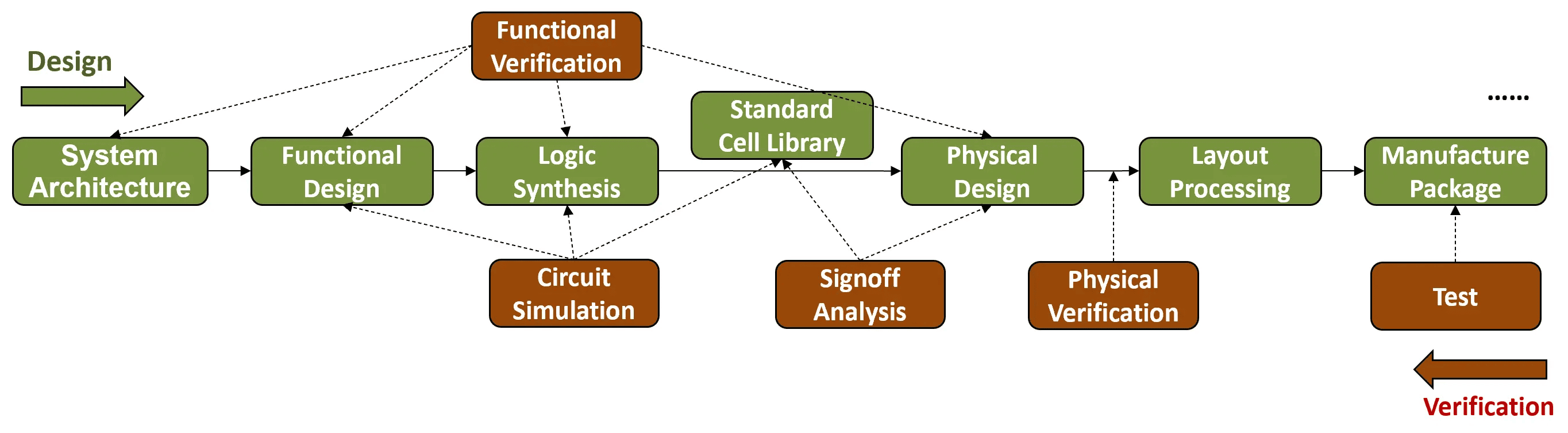

图2 主要EDA工具步骤

iEDA课题组主要的研发重点关注在芯片逻辑综合,物理设计,签核分析和物理验证环节,如下图绿色部分所示:

图3 iEDA工具聚焦领域

3 "wafer" "chip" "die" 的联系和区别

一、名词解释:

wafer:晶圆;是指硅半导体集成电路制作所用的硅晶片,由于其形状为圆形。

chip:芯片;是半导体元件产品的统称。

die:裸片 ;是硅片中一个很小的单位,包括了设计完整的单个芯片以及芯片邻近水平和垂直方向上的部分划片槽区域。

二、联系和区别:

一块完整的wafer

wafer为晶圆,由纯硅(Si)构成。一般分为6英寸、8英寸、12英寸规格不等,晶片基于wafer上生产出来。Wafer上一个小块晶片晶圆体学名die,封装后成为一个颗粒。一片载有Nand Flash晶圆的wafer首先经过切割,测试后将完好的、稳定的、足容量的die取下,封装形成日常所见的Nand Flash芯片。

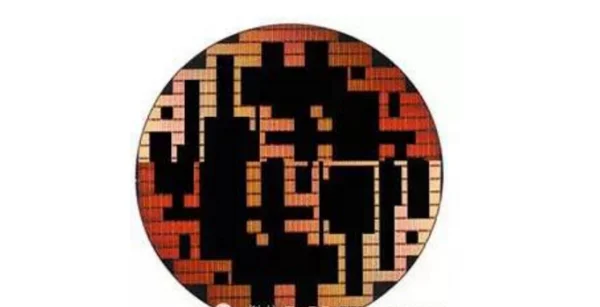

die和wafer的关系

品质合格的die切割下去后,原来的晶圆成了下图的样子,是挑剩下的Downgrade Flash Wafer。残余的die是品质不合格的晶圆。黑色的部分是合格的die,会被原厂封装制作为成品NAND颗粒,而不合格的部分,也就是图中留下的部分则当做废品处理掉。

筛选后的wafer

扩展资料:

集成电路芯片的生命历程:芯片公司设计芯片——芯片代工厂生产芯片——封测厂进行封装测试——整机商采购芯片用于整机生产。

芯片供应商IDM:是集芯片设计、制造、封装和测试等多个产业链环节于一身的企业。

芯片供应商Fabless:是没有芯片加工厂的芯片供应商,Fabless自己设计开发和推广销售芯片,与生产相关的业务外包给专业生产制造厂商。与Fabless相对应的是Foundry和封测厂,主要承接Fabless的生产和封装测试任务,封测厂有日月光,江苏长电等。

4 引用

[1] https://teamvlsi.com/2020/05/asic-design-flow-overview-v1.html

[2] https://zhuanlan.zhihu.com/p/380962676

[3] https://yearn.xyz/docs/vlsi-后端设计/70-vlsi-后端设计-简介/

[4] https://zhidao.baidu.com/question/2040027.html