3.3 布局阶段

布局范畴的I/O单元和模块的布放都在布图规划时完成了,并且决定了布局方案——展平式布局 or 层次化布局,因此布局的剩余任务主要是根据布局方案对标准单元进行布局。标准单元具体的种类和功能请移步第4部分。

1 布局的内容

Placement详细步骤

(1)Initial placement

这个步骤就是通常我们所说的初始布局,也称Coarse placement。在这一步骤中,EDA工具会根据设计规约和布局约束,将电路中的元件(如逻辑门、存储器等)初步放置在芯片的物理空间上。这一放置是基于初始算法进行的,通常不是最优的。此时不考虑overlap问题。Overlap问题是指在电路布局中的一个常见挑战,即不同电路元件(如逻辑门、存储器等)在物理空间上的互相重叠或冲突。

(2)Legalization

有了第一步的coarse placement后,这步需要将粗略摆放好的cell,进行合法化(legalization)操作,将所有的标准单元放置在row上,并且保证所有的cell处于legal的状态,即不存在overlap或者不在对应的row上。合法指的是调整单元元件位置、间距、对齐等,以确保布局满足电路设计要求,并且不会产生冲突。

(3)Removing existing buffer trees

这步称 Removing existing buffer trees (移除现有缓冲树)。在某些电路中,为了解决时序问题和信号延迟,可能会添加缓冲器。但在布局过程中,为了减少功耗和信号线长度,可能会决定移除一部分缓冲器。这一步骤涉及移除布局中的部分缓冲树,并重新布置相关元件。

(4)High Fan-out Net Synthesis (HFNS)

在电路布局中,高扇出网络综合(High Fan-out Net Synthesis,简称HFNS)是一个重要的步骤。它主要针对具有高扇出的点(除了时钟信号、复位信号等特殊情况)进行优化,以改善电路的时序性能。在进行HFNS之前,有一些设计方面的限制需要考虑,并尽可能去除不必要的理想网络,以提高布局质量。

(5)Iterations of timing/power optimizations

这步称 Iterations of Timing/Power Optimizations(时序/功耗优化迭代)。在此阶段,通过迭代优化技术来改进电路的时序和功耗。这包括对关键路径的延迟进行优化、对逻辑元件进行重新布局优化以减少功耗、调整元件位置和布线等。迭代优化的目标是满足设计的时序约束和降低功耗。这个过程主要有cell sizing, moving, net spitting, gate cloning, buffer insertion和area recovery这些小步骤组成。

(6)Scan-chain re-ordering

scan chain reordering (扫描链重新排序)并不是每个设计中都要做的,视不同的情况而定。这个过程主要是用来缓解绕线资源紧张问题。扫描链是用于测试和故障排除电路的重要组成部分。这一步骤涉及对扫描链的重新排序,以优化测试时间和故障覆盖率。重新排序可以通过调整扫描链中元件的顺序来实现。

2 布局的目标评估

布局完成后,如何评估布局的好坏呢?在满足设计规则的要求情况下(即除了时钟网络,其他的高扇出网络,如复位信号等都插入了相应的驱动单元,从而满足最大电容、最大扇出和最大信号转换时间等设计约束。时钟网络上的设计规则需要在时钟树综合阶段完成),可以归纳为一下3个部分:

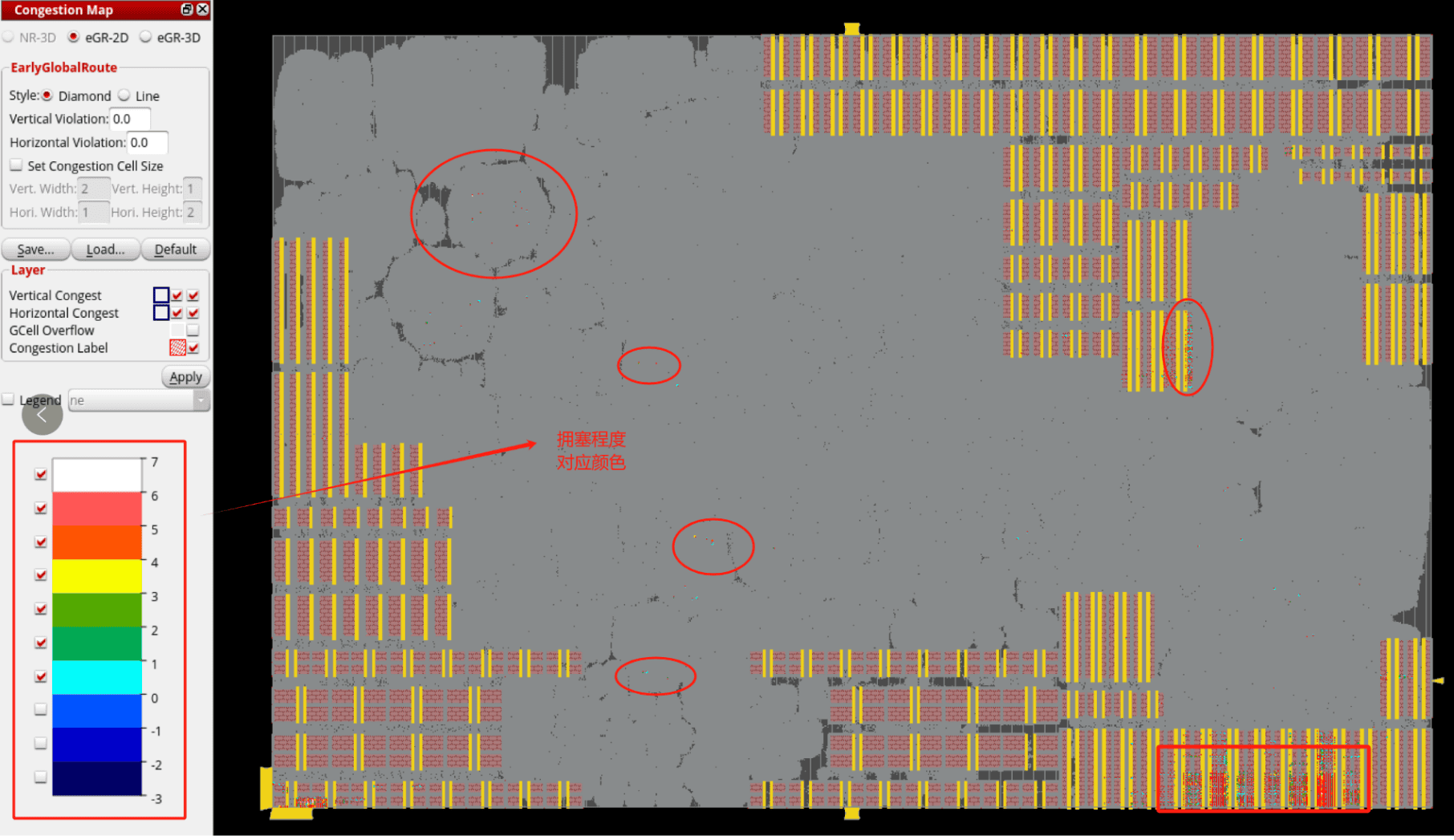

拥塞预估

要求满足布线布通。 EDA工具将整个布线空间划分为多个小的布线格,每个布线格划分为横向通道和纵向通道,在每个布线格内,估算并统计所需要的纵向通道和横向通道数量,当实际需要的通道超过现有的通道的5%时,表明拥塞程度比较大。由EDA工具分析拥塞和显示拥塞程度的菜单,可以得出拥塞的数据和分布,从而决定布局优化的方案。当全局拥塞很小,但是存在局部拥塞较大的情况时,则需要对设计进行优化。当报告全局的拥塞非常小,但是在局部区域存在着较大的拥塞,会造成布线无法布通时,则需要对标准单元布局进行优化。

时序预估

要求满足建立时间要求。 标准单元布局完成后,其位置都相对确定,此时对芯片的延迟计算和时序较接近于芯片最终的时序。在布局完成后,一般只需要做建立时间(setuptime)预估,不需要做保持时间(holdtime)预估,因为此时还没有进行时钟树综合,而保持时间的违例通常是在时钟树综合之后进行优化。

这时还可以对噪声的影响进行预估,在0.18um及以上工艺,一般不需要太多地考虑噪声,而在 0.13um及以下的工艺中,则需要考虑噪声的影响,在标准单元布局阶段即可以考虑噪声。

供电预估

要求标准单元可以顺利供电。 标准单元布局后,将标准单元的供电端口连接到电源网格中(followpins),此时可以引用VCD文件,对芯片的功耗、电压降及EM进行评估。由于时钟树还没有综合,功耗值会偏小,在预估时应当注意。