4.3 天线效应

MOS晶体管的栅氧化物是MOS器件中最敏感的部分。在ASIC的制造过程中需要特别小心,以保护它免受制造过程和ASIC运行过程中的任何损坏。天线效应是一种现象,可能会在制造过程中对MOS的栅氧化物造成损害,特别是由于等离子刻蚀过程。在本文中,我们将详细调查天线效应现象及导致该效应的原因。

1 什么是天线效应?

天线效应这个术语可能不会给您正确的直观感受,可能让您联想到电磁辐射或发射-接收概念,但这里情况不同。因此它还有另一个流行的名称,即“等离子诱导栅氧化物损伤”,这为该效应提供了正确的直觉。正如该名称本身所示,这是由于等离子刻蚀过程中对栅氧化物造成的损害所引起的效应。

在芯片制造过程中,MOS管的栅氧化层上连接了一大片的导体,当进行离子刻蚀时,那个大片导体像一根天线一样,不断地收集电荷,使得导体上的电压越来越高,最终击穿MOS管的栅氧层,使MOS管失效,这就是天线效应(PAE,process antenna effect)。

在芯片制造流程中,首先进行前端制程(FEOL),涉及所有MOS晶体管的制造。一旦FEOL制程完成,就开始进行后端制程(BEOL)的制造,涉及金属互连的制造。天线效应出现在BEOL制程时。

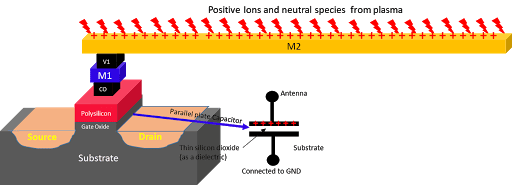

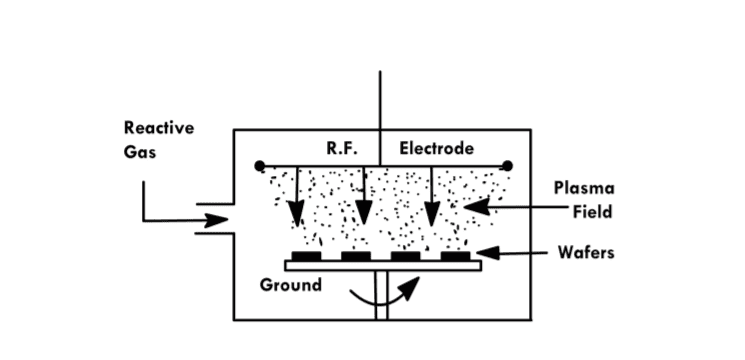

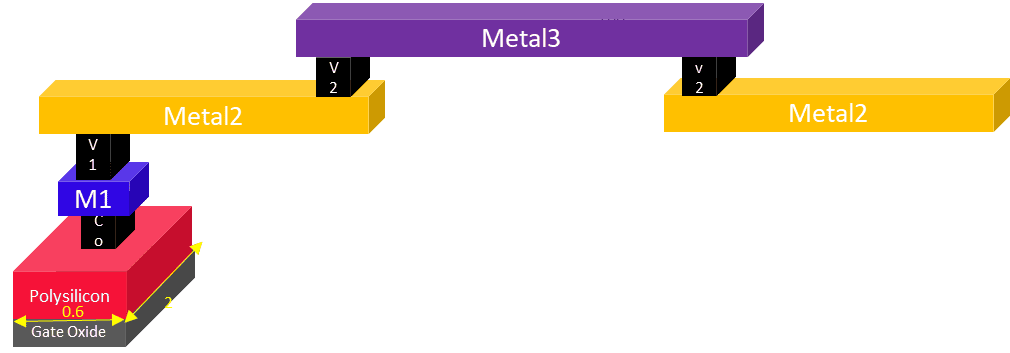

在集成电路制造过程中,等离子刻蚀工艺用于制造金属互连。等离子刻蚀是一种干法各向异性刻蚀过程,用于选择性刻蚀。等离子含有高能离子和自由基,在金属刻蚀过程中会被金属互连收集。图1显示了MOS结构和等离子被互连收集的结构。

图1 MOS结构和等离子体刻蚀

图1 MOS结构和等离子体刻蚀 电荷积累的数量取决于互连的表面积。这些收集的离子增加了互连的电位,如果互连连接到多晶栅,最终会增加栅极的电位。由于栅极电位的增加,可能会通过栅极氧化物形成漏电路径到衬底,以平衡栅极上额外积累的电荷。如果积累的电荷量较大,通过栅极氧化物的漏电路径可能会破坏栅极氧化物,导致MOSFET永久损坏,或者在栅极氧化物中产生电荷捕获,进而导致许多副作用,如早期栅极氧化物破坏、迁移率下降和阈值电压偏移。

栅极氧化物损坏主要是由于金属互连的等离子刻蚀引起的,因此这种效应也被称为“等离子诱导栅极氧化物损伤”或“天线效应”。收集等离子体(离子)并连接到栅极的金属互连基本上被称为天线。

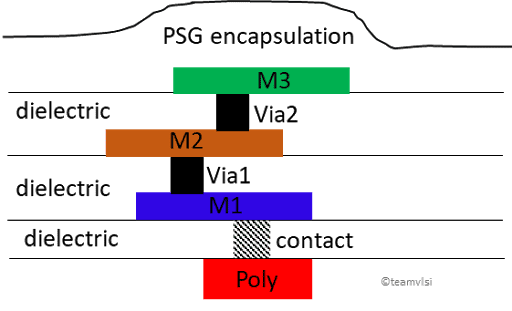

(1) 互连制造过程

在多晶硅上,沉积一层介质,然后进行接触切割。在接触上,沉积金属-1并进行图案化和刻蚀多余的金属,并用介质填满整个区域。在制造金属-2之前,对通过介质进行切割并用通过介质填充,然后在通过介质上沉积金属-2。同样的方式再次进行金属2的刻蚀,并用介质填充。这个过程将根据金属层数的数量重复多次。在所有金属处理结束时,进行PSG封装如图所示。

对于每个金属层,通过相应的通孔/接触,基本上执行三个步骤。

- 沉积

- 刻蚀

- CMP

在第一步中,金属被沉积,第二步中,不需要的金属区域被刻蚀掉,第三步,进行CMP(化学机械抛光)。

现在让我们更多地谈谈刻蚀过程。基本上有两种刻蚀过程,一种称为用化学品进行湿法刻蚀,另一种是用气体进行干法刻蚀。干法刻蚀提供完全的各向异性刻蚀,其中横向刻蚀速率为零。最受欢迎的等离子刻蚀是一种干法刻蚀过程,下面简要介绍。

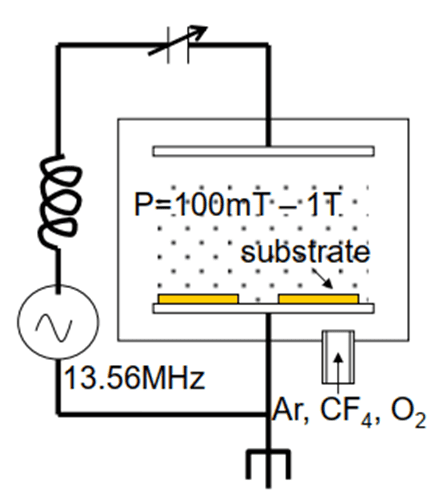

(2) 等离子刻蚀

这里将简要介绍等离子刻蚀过程,以便了解该过程。等离子刻蚀涉及以适当的气体混合物高速喷射到样品的等离子体流。等离子源称为蚀刻物种,可以是带电离子、中性原子或自由基。在蚀刻过程中,等离子体从目标材料与等离子体生成的反应性物种之间的化学反应中产生挥发性蚀刻产物。等离子刻蚀的基本设置如下图所示。

图2 等离子刻蚀设置

图2 等离子刻蚀设置  图3 半导体制造中的等离子刻蚀过程置

图3 半导体制造中的等离子刻蚀过程置 顶部和底部电极大小相等且平行。底部电极固定晶圆并接地。由于施加了射频电压和高压(P=100mT至1T),在两个电极之间建立了等离子体。高能电子与气体分子反应,并产生各种反应性物种、中性物种和离子。中性物种提供化学刻蚀,离子提供物理刻蚀,反应性物种和离子的组合提供离子增强刻蚀。

2 天线效应产生的条件

① 发生在芯片制造过程:在运输,存储,和应用时不会发生。

② 发生在离子刻蚀时:只有在离子刻蚀时才存在带电的粒子,悬空的导体会吸收这些带电的粒子产生电压。

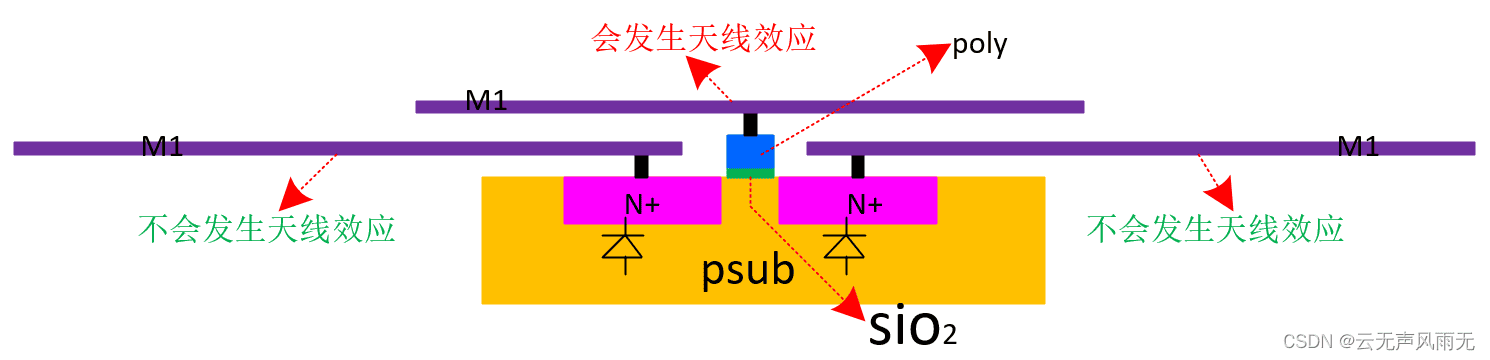

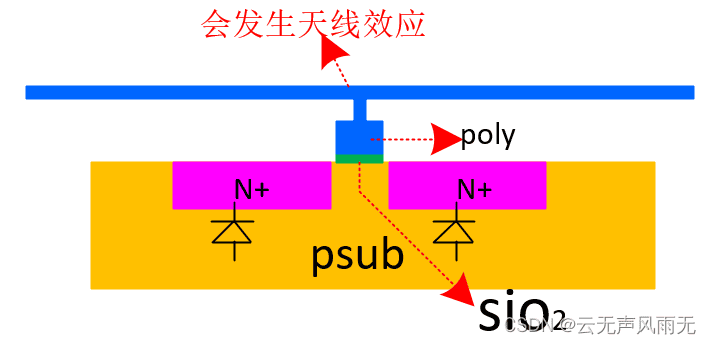

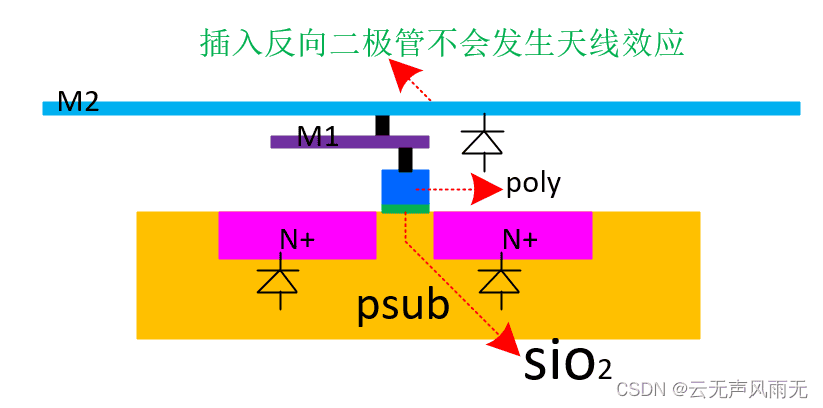

③ 发生在栅氧层上:栅氧层是一层薄膜sio2,当栅极的悬空导体吸收了大量的带电粒子后,栅极电位被抬高,最后可能会击穿栅氧。源极和漏极不会发生天线效应,因为源漏极不存在sio2隔离层,直接contact打到金属层,加上其本身存在寄生二极管,可以将源漏上悬空的导体收集的电荷泄放掉,从而不会对源漏造成损伤。

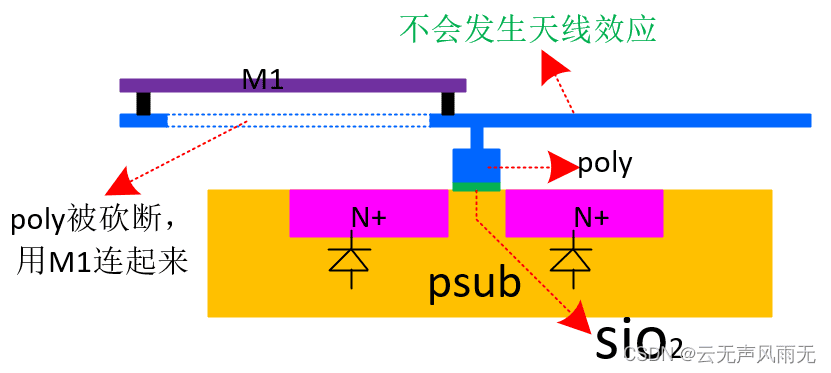

④ 栅氧上必须要有大片导体:导体包括多晶硅poly层和金属层,因为poly和金属都是可以导电的,大面积的poly和大面积的金属都会导致天线效应。Layout上应该注意不要使用poly连长线,poly发生天线效应只能够将其砍断,改用金属连线才可以防止,加泄漏二极管是没有意义的,因为二极管需要通过金属连出电极,最后还是得经过过孔连到poly上,在刻蚀poly时金属还未做,此时二极管压根没连到poly上,起不到泄放电荷的作用。

3 产生天线效应的评估条件

尽管天线效应发生在芯片的制造阶段,特别是在等离子刻蚀过程中,但预防机制应该在物理设计阶段设定。制造实验室提供了天线规则文件,必须在物理签核阶段进行检查,设计应按照天线规则进行清理。DRC规则中一般用天线比率来判断是否会发生天线效应。天线比率是指连接到同一点的导体面积和栅氧面积之比。通过DRC的antenna rule可以检查出来违反天线效应规则的net。

4 如何预防天线违规?

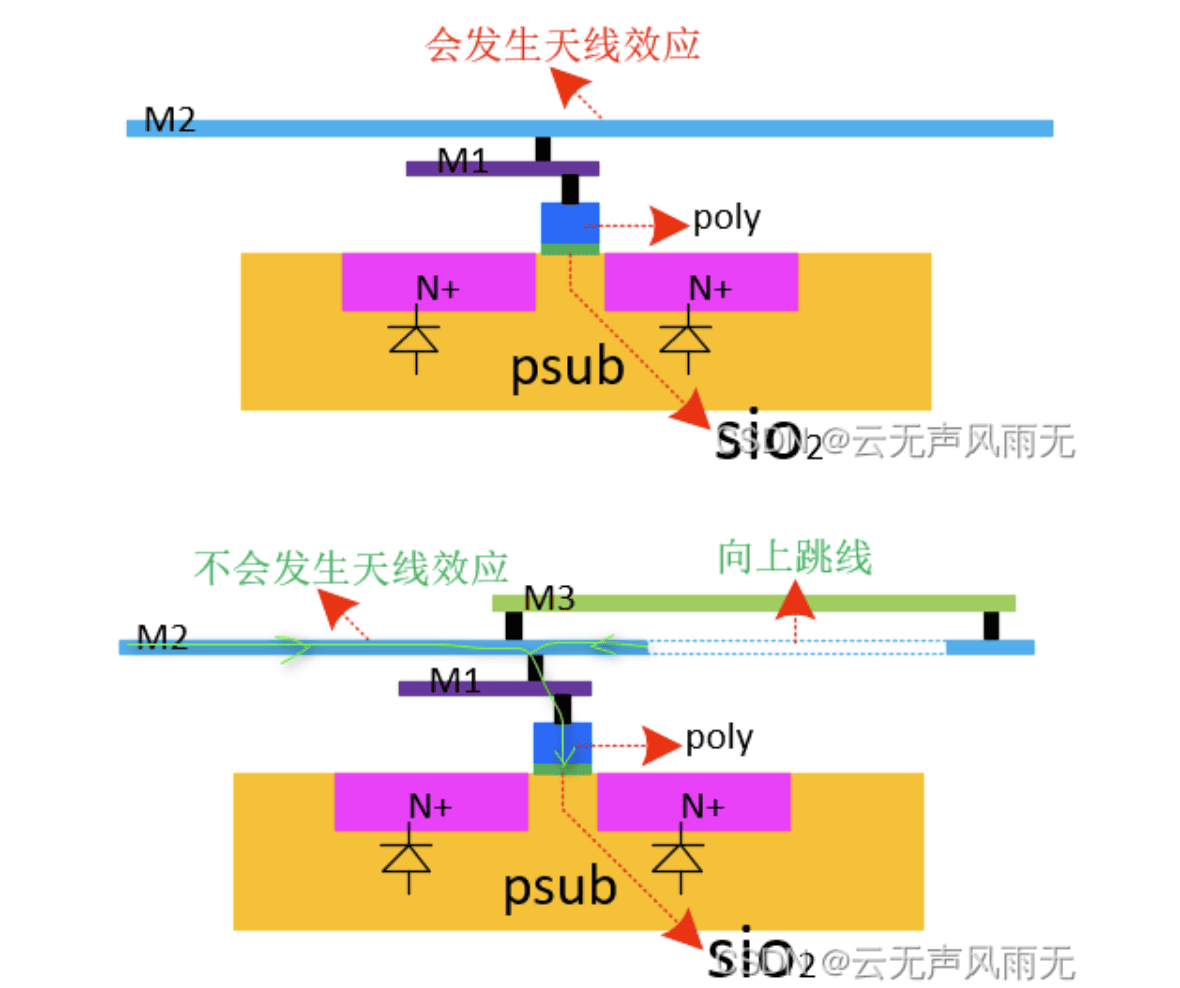

在讨论预防之前,让我们回顾一下天线效应的根本原因,然后理解预防技术将变得容易。天线效应主要是由于等离子体刻蚀金属互连过程中与晶体管栅极连接的金属互连上过多的电荷积累所致。积累电荷的数量取决于与栅极连接的金属互连的面积。过多积累的电荷通过薄栅氧化物被释放,并导致栅氧化物永久损坏。

基于上述天线违规原因,可以采用以下三种方法来预防该问题。第一种方法是通过减少与晶体管栅极连接的金属互连的面积来减少电荷积累。第二种方法是增加栅区面积,使得(金属面积)/(栅区面积)的比值小于允许的最大金属对栅区面积比。这可以通过将浮动栅连接到相关网络来实现。第三种方法是为排放晶体管栅极上积累的电荷提供替代路径,即添加天线二极管。

预防天线违规的三种基本技术如下:

- 金属跳跃

- 浮动栅连接

- 天线二极管

现在重要的是了解天线规则和违规情况。我们将在查看天线规则后回到这一点。

(1) 天线规则

流程设计工具包(PDK)附带一些规则文件。天线规则集是规则文件的一部分。在提交前必须检查所有规则集。在天线规则中,最常见的规则是天线比。

- 天线比是连接到栅极的金属面积与栅总面积之比。

- 天线比的定义如下:

- 天线面积 / 栅面积 < 最大天线比

天线规则违规示例:

考虑以下三种情况:

案例1:假设金属2的长度为200μm,宽度为1μm,如上图所示,这根金属导线连接到一个晶体管的栅极。该晶体管的栅宽度为2μm,长度为0.6μm。

因此:

- 总金属面积= 200×1 = 200μm^2

- 总栅面积= 0.6×2 = 1.2μm^2

- 天线比= 200/1.2 = 166.2

案例2:假设情况与案例1相同,但金属2连接到4个晶体管而不是1个。

- 总金属面积= 200×1 = 200μm^2

- 总栅面积= 0.6×2×4 = 4.8μm^2

- 天线比= 200/4.8 = 41.66

案例3:假设金属2被分成两段,每段50μm,并通过金属3连接,如下图所示。这种连接称为金属跳跃。

- 总金属2面积=(50×1)×2 = 100μm^2

- 总栅面积= 0.6×2 = 1.2μm^2

- 天线比= 100/1.2 = 83.33

假设天线比规定为100。因此,在上述三种情况中,案例1违反了天线规则,而案例2和案例3没有违反天线规则。

(2) 如何修复天线违规

上述示例显示,如果通过增加连接的晶体管数量来增加栅面积,将减少天线比。另一种方法是通过减少天线面积来修复天线违规,即在金属之间断开并插入跳线。因此,我们可以通过两种方式减少天线比:

- 减少天线面积-插入跳线或金属跳跃

- 增加栅面积-插入虚拟晶体管

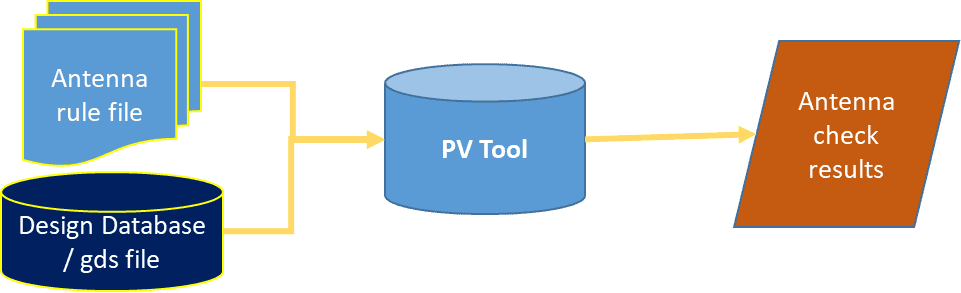

天线检查(物理验证)

- 天线检查验证布局是否符合规则文件中的天线规则。在提交之前,还需要执行许多其他检查,如DRC、ERC、LVS等,这些统称为布局的物理验证。

- 物理验证工具(如Calibre,Assura,IC Validator)针对适用天线规则的所有层验证天线规则。

- 天线规则在很大程度上依赖于工艺节点。

天线违规修复措施

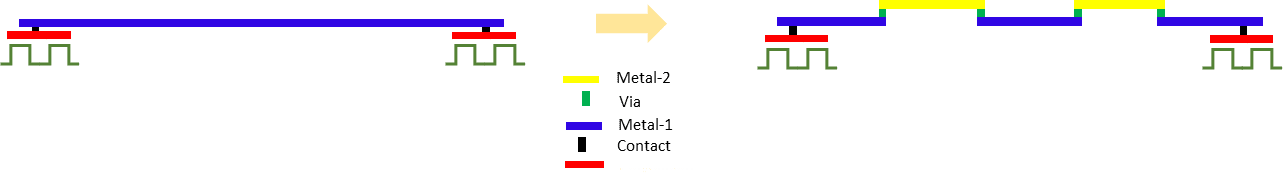

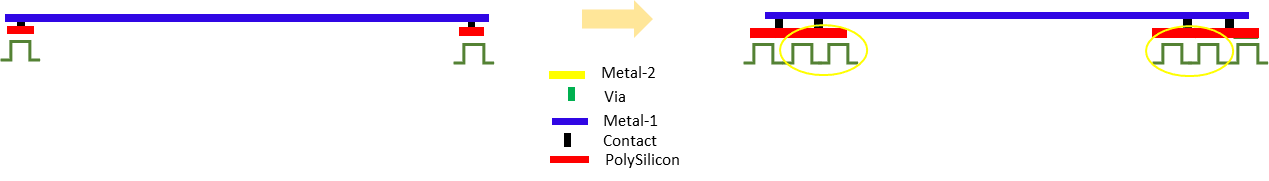

1. 插入跳线或金属跳跃

切断长的走线,向上跳线,当该层金属收集电荷时,上层金属还未做,相当于减少了天线的面积,可以防止天线效应。这种方法会增加走线复杂度,而且在高速信号时还会影响时序。

特别注意:向下跳线不能解决天线效应,应为当该层金属收集电荷时,下层金属已经做好了,并将切断的该层金属连在一起,并未减少了天线的面积,因此不能防止天线效应。

2. 插入虚拟晶体管

如上图所示,可以通过插入虚拟晶体管来增加有效栅面积。这将降低天线比并有助于满足天线规则。在实际情况中,我们可以添加一个浮动的反向器/缓冲器。我们将缓冲器/反向器的输入连接到相关网络,并将输出保持浮动。这将增加有效栅面积并有助于解决天线违规问题。实质上是减小天线面积,但是会增加信号的延时,对时序要求比较高的电路不适用。而且,这种方法不适用于模拟信号,只适用于数字信号。

3. 插入反向二极管

芯片正常工作时,二极管处于反偏状态,不会影响电路功能。当发生天线效应时,反偏二极管优先MOS击穿,将天线上收集的电荷释放掉,达到保护MOS管的作用。一般stdcell中会提供这种防天线的二极管器件,在原理图和layout中添加进去即可。如果没有的话,可以自己手画一个,或者是调用一个pdk中的二极管,需要注意的是要保证正常工作时二极管处于反偏的状态,或者会出现漏电或者功能不正常等问题。 使用这种方法可能会增加芯片面积,需要综合考虑。

谢谢

https://teamvlsi.com/2020/05/latch-up-prevention-in-cmos-design.html

https://zhuanlan.zhihu.com/p/660374839

https://blog.csdn.net/al20093064/article/details/133715942

https://teamvlsi.com/2020/06/antenna-prevention-techniques-in-vlsi.html