4.1 闩锁效应

闩锁效应用一句话来讲,即:如果芯片中出现了某种寄生结构,某种触发机制会使得电源轨之间形成低阻抗路径,从而形成的大电流损坏正常的电路功能部分。PNPN结构是形成闩锁效应的一种寄生结构,但归根到底,罪魁祸首是PNP、NPN组成的SCR(Silicon Controlled Rectifier)结构。接下来,将从SCR结构出发,讲述闩锁效应的形成以及预防。

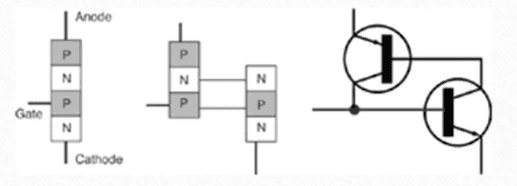

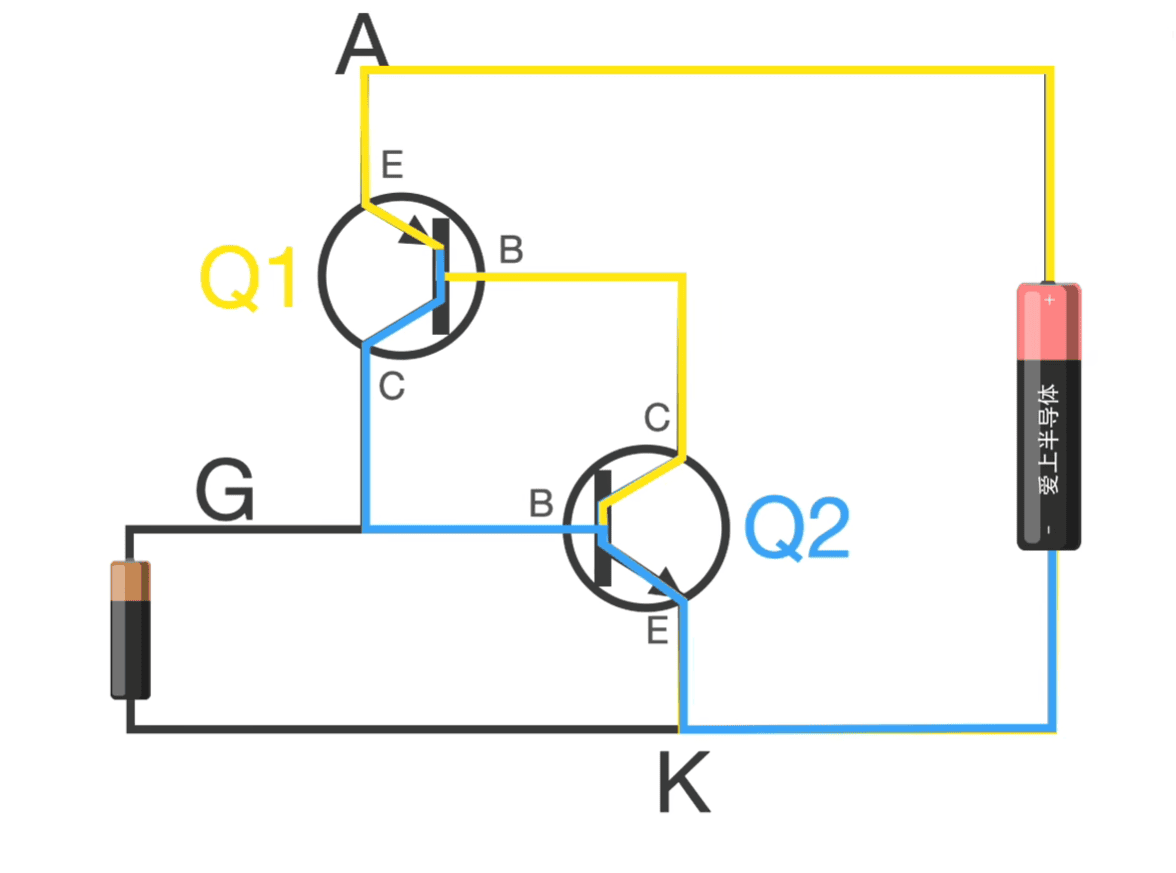

图1 左侧:PNPN结构;右侧:SCR结构

1 预备知识:三极管

对三极管原理很熟悉的同学,可以跳过这一节。三极管的作用:实现小电流控制大电流。

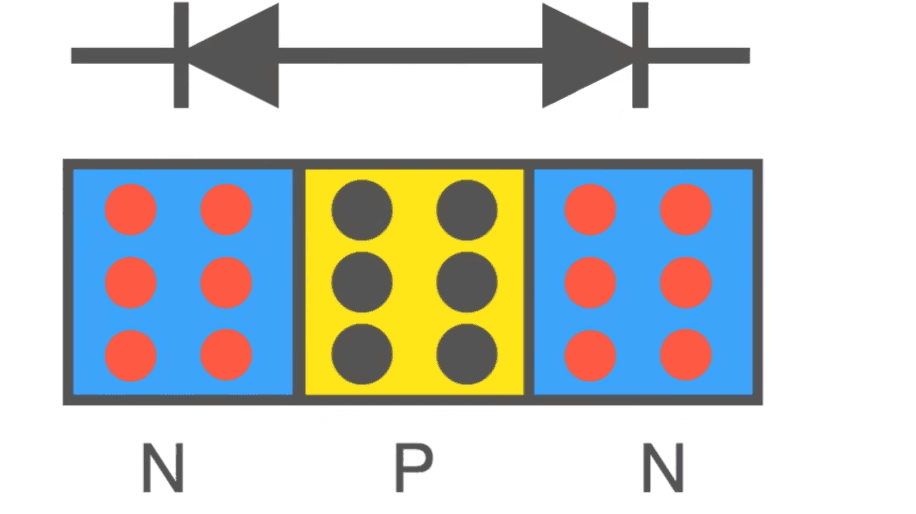

图2 NPN型三极管与PNP型三极管

如下图所示,这是一个NPN型三极管。N型半导体有很多空穴,P型半导体有很多自由电子。此三极管形成了两个PN结,无论通哪个方向的电,三极管都会截止。可以将左侧N型半导体称为发射区,中间P型半导体称为基区,右侧N型半导体称为基电区。

图3 NPN型半导体

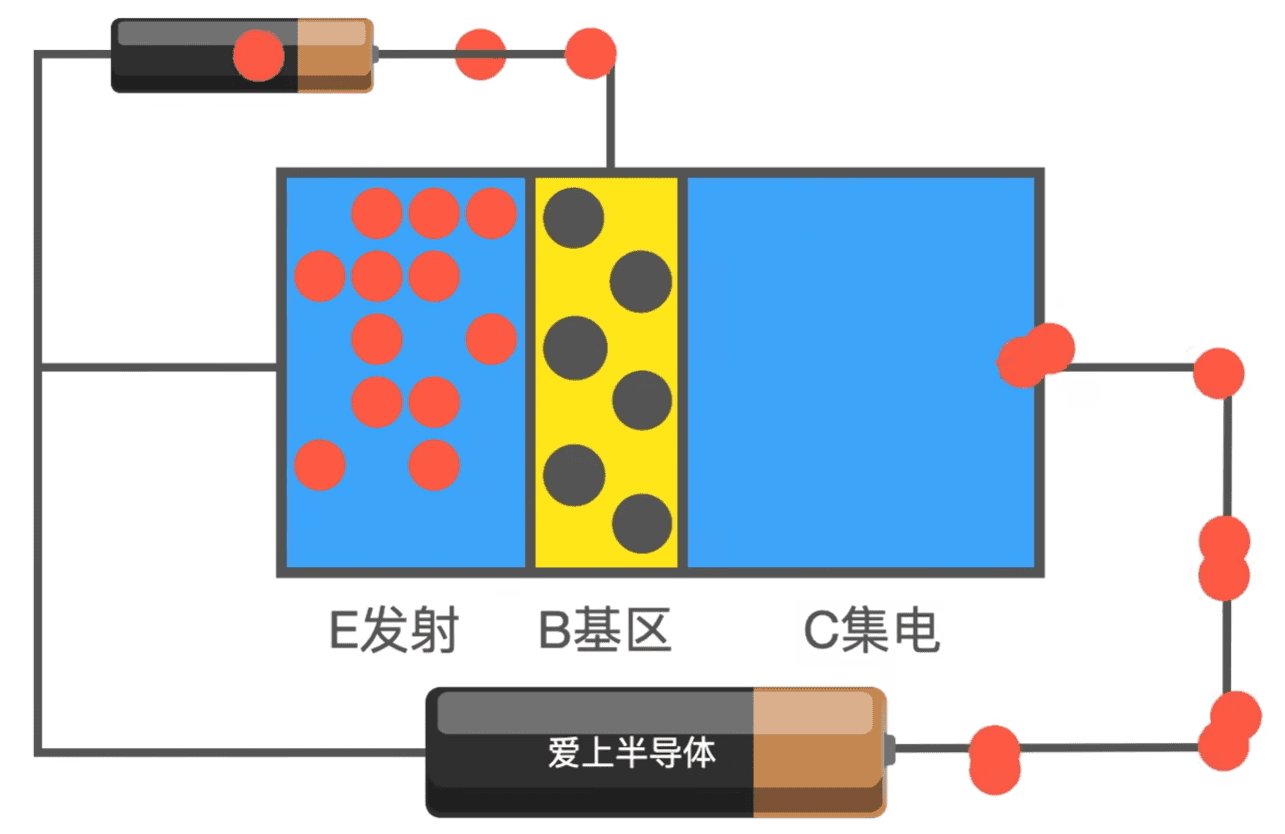

向E发射区和B基区通电,E发射区的少部分电子与B基区空穴复合,形成基极电流。大部分电子会吸引到集电区,形成集电电流,也就是三极管的输出电流。

图4 三极管的导通

更多三极管的知识,可点击这里查看文字,或者点击这里查看视频。

2 预备知识:晶闸管

像三极管或者mos管,输入高电平时则导通,撤离高电平则截止。但是对于晶闸管,输入高电平时导通,撤离时依然导通。产生闩锁效应的SCR(可控硅整流管)是晶闸管中的一种,属于半控器件。因此,可控硅可以控制电路的导通,却不能控制电路的关断。 对晶闸管熟悉的可跳过这节。

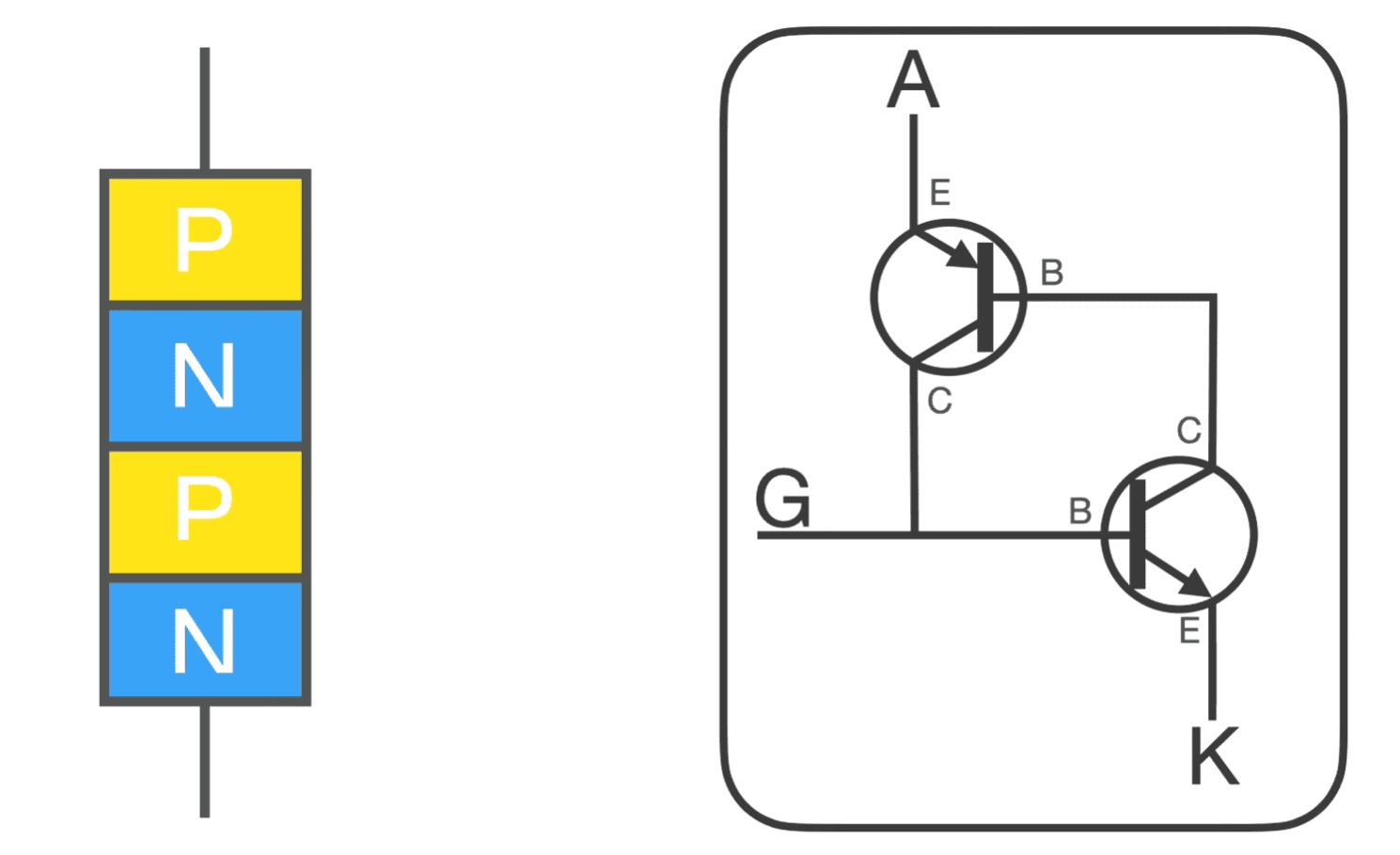

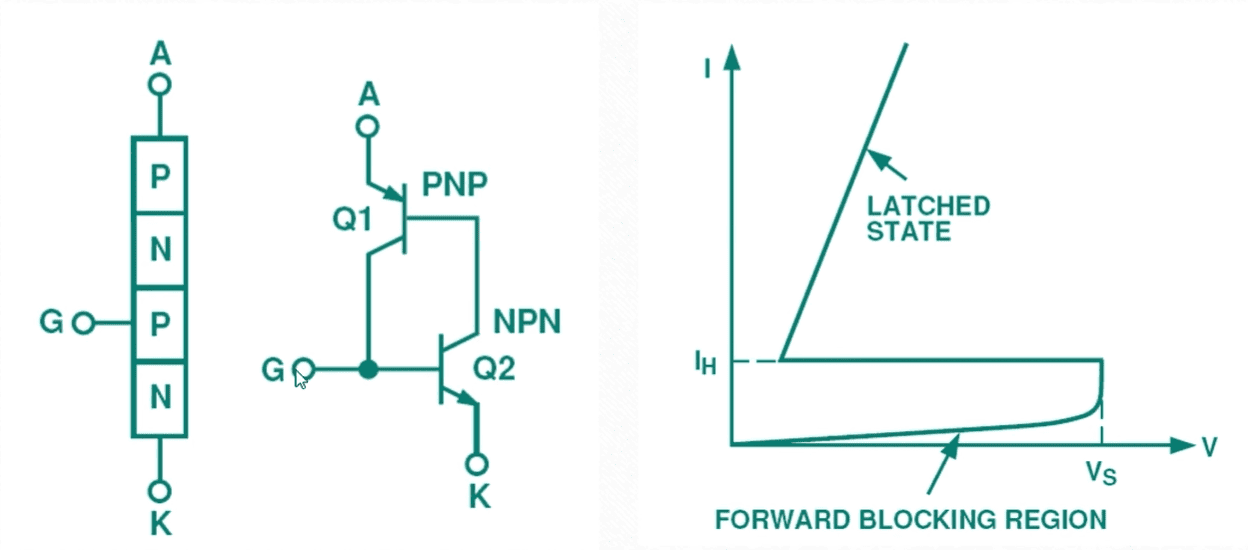

图5 SCR的结构

PNPN结构相当于将三极管PNP结构与三极管NPN结构连接在一起。图5右侧即为PNPN的等效电路符号。 当在G极接入电压,Q2导通,Q1的B极电流形成回路,Q1导通,C极输出的电流使B极形成回路,而不依赖G极的接入电压。当G极电压撤离,依靠C极输出电流形成B极回路,Q2依然导通,因此Q1也导通,整个电路依然导通。

图6 SCR原理

需要注意,A极称为阳极,K极称为阴极,G极称为控制极。

3 闩锁是如何形成的

(1) 闩锁产生机制

图7 闩锁产生机制

此时的SCR是寄生的结构,非设计生成的。可以看出它是由PNP型三极管和NPN型三极管组成的,正常情况下处于关断状态。G极上的毛刺触发使得SCR进入Latchup,相当于在NPN三极管形成E区与B区的基极电流,根据三极管特性,形成集电电流,Q2打开。同理打开Q1。

流程:

Q2的G极电流注入Q2基极 -> Q1基极射极产生电流 -> Q1打开 -> 更多的电流注入Q2基极 -> 形成正反馈 -> Q1Q2饱和。一旦触发Latchup,即使去掉G极上的信号也不会退出Latchup状态。

推出机制:

要退出Latchup,要么SCR两端的电压减小到某个值,要么流过的电流小于IH

(2)SCR结构的形成

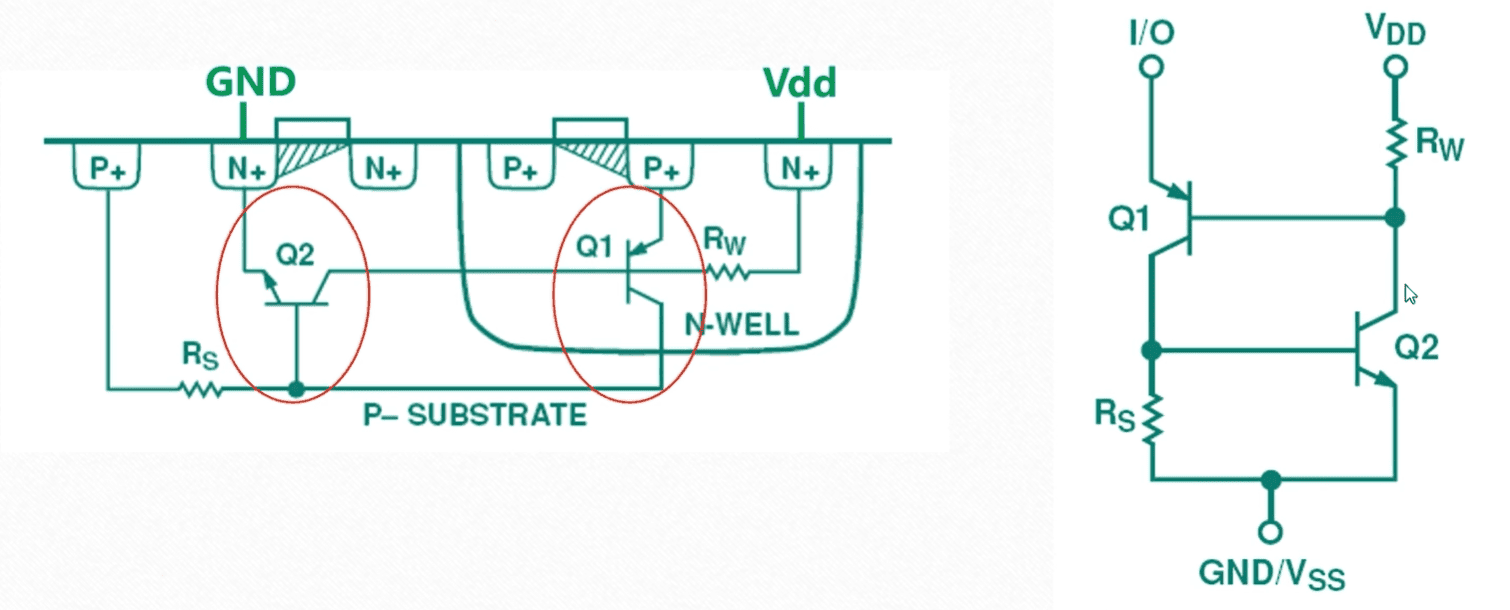

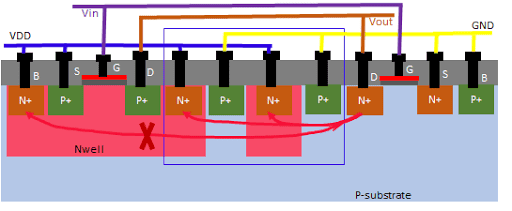

图8 SCR结构的形成

在CMOS(互补金属氧化物半导体)电路内部,会形成两个寄生的BJT(双极晶体管),并以一种这样的方式连接起来,使得这些BJT形成一个PNPN器件或SCR(可控硅)或晶闸管。

如上图所示,在n型井上形成了一个pMOS器件,而在p基片区域形成了一个nMOS器件。如果我们看到pMOS器件的源或漏极下方的区域,源或漏极是通过P+植入形成的,然后是n型井,再下面是p基片。因此,在这里形成了一个寄生的PNP BJT,其发射极是pMOS的源极,基极是n型井,集电极是p基片。类似地,在nMOS器件附近形成了一个寄生的NPN BJT,其发射极是nMOS的源极,基极是p基片,集电极是n型井。

这两个BJT以一种使它们形成PNPN器件的方式相互连接。PNP BJT的基极连接到NPN BJT的集电极,而NPN BJT的基极连接到NPN BJT的集电极。

PNPN器件通常处于关闭状态,并且通过它的电流非常小或没有。但是一旦PNPN器件由其门信号触发,就会开始有大电流通过它,并且即使去除了门信号,它也会继续流动。下图显示了PNPN器件的端子和特性。

总结:

Q1和Q2都不是设计出来的,而是寄生形成的:

- 寄生Q2 NPN的形成:P衬底是基极,N+阱是射极,其他不相关的N+阱是集电极

- 寄生Q1 PNP的形成:N+阱是基极,P+是射极,P衬底是集电极

- SCR被触发后,VDD提供电流,电流不加限制,会损坏芯片

2 闩锁的触发机制及预防

(1)闩锁的触发机制

数字芯片:输入输出管脚上的正脉冲或负脉冲信号,超过电源轨一个二极管压差时,有可能会发生闩锁。

模拟芯片:像放大器,在输入超过供电轨,或电源上电不同时,会发生门锁。

CMOS内部形成的PNPN器件可以通过各种方式触发。一旦PNPN器件通过任何方式被触发,Latch-up事件就会开始。以下是一些主要原因。

- 输出端口的噪声

- 静电放电(ESD)事件

- 电离辐射

假设由于噪声,输出电压已经超出了VDD,那么它将正向偏置pMOS的漏极和n型井之间的晶体管。一旦这个结正向偏置,P+区域就会开始向n型井注入空穴,这些空穴将被nMOS的body接触收集,因为它连接到GND。因此,这个事件将导致从pMOS的漏极到nMOS的body流动电流。由于上述电流的流动,nMOS的源端和其下面的基片之间将产生电压降。它将正向偏置nMOS的源和基片之间的pn结。这将再次开始从N+源向基片注入电子,这些电子将被连接到VDD的pMOS的body端收集,如红色虚线所示。因此,最终将启动一个链,接下来pMOS的源端和n型井将被正向偏置。以此方式,这两个二极管都被打开并形成了latch-up。

类似地,如果输出电压低于VDD,首先nMOS的漏极和基片之间的结将被正向偏置,然后它会使pMOS的源和n型井之间的结正向偏置,进一步使nMOS的源和基片之间的结正向偏置,这将使得两个BJT都打开并产生latch-up。

(2)闩锁的预防

在讨论Latch-up问题的预防技术之前,让我们首先回顾Latch-up问题的关键因素。以下两个因素对Latch-up问题至关重要。

- n-well和p-substrate的高电阻

- β1 x β2 > 1

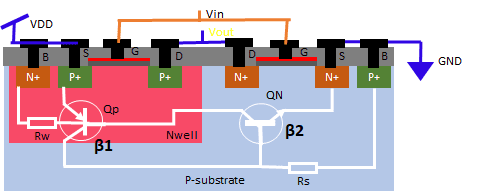

图9 Latch-up的形成

图9显示了导致Latch-up的寄生BJT形成。n-well和p-substrate的电阻可以通过增加掺杂来减少,但这会严重降低器件性能。但是,我们可以减小寄生BJT的增益(β),从而防止Latch-up问题。一些流行的Latch-up预防技术如下。

- 防护环

- 井接地单元

- 隔离沟槽

- 外延层

- 逆向井掺杂

- 外延层和逆向井掺杂的组合

- mFDSOI技术

- ESD保护技术

1. 防护环:

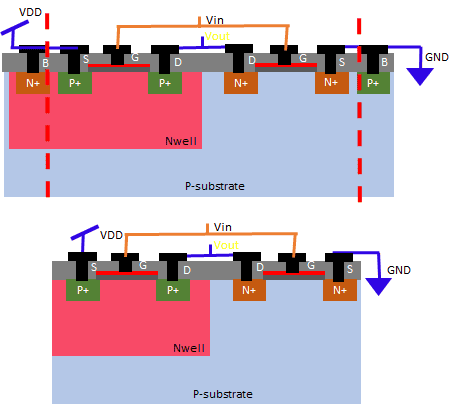

图10 防护环

如果输出电压低于VSS,并且nMOS的漏极与p-substrate之间的二极管变为正向偏置,那么来自漏极的电子开始注入到substrate中,并被pMOS的body收集。这会导致一个与电子流方向相反的电流。最终触发图9中所示的Qp晶体管。为了打破这种链条,在n-well中添加两组n+注入物,同时在p-substrate上添加p+注入物,如图8所示。这些将收集从nMOS漏极注入的电子,并阻止来自nMOS漏极流向pMOS body的电流。这样就阻止了触发Qp BJT。

类似地,如果输出电压高于VDD,并且pMOS的漏极开始向n-well注入空穴并被nMOS的body收集,那么会触发Qn BJT。但是通过添加防护环,这些空穴将被防护环收集,并阻止Latch-up。

2. 井接地单元:

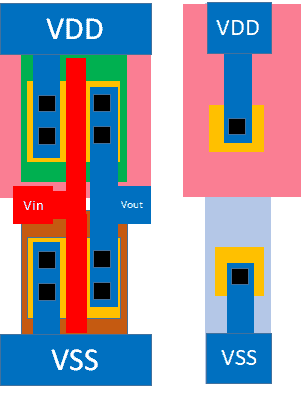

在无接地标准单元设计中,为了防止Latch-up,我们需要将n-well接地到VDD,将p-sub接地到VSS。这些井接地单元将n-well接地到VDD,p-sub接地到VSS。图11显示了无接地单元和有接地单元的横截面,图12显示了井接地单元和无接地标准单元的布局。

图11 井接地电池和无接地电池的横截面

图12 无接地电池和井接地电池的布局

井接地电池按照技术库中定义的最大距离规则,在标准单元行中以固定间隔放置。

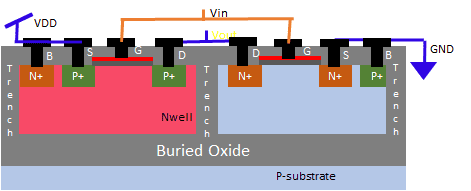

3. 氧化物沟槽隔离:

在这种技术中,nMOS和pMOS使用埋氧化物和氧化物沟槽进行隔离。深处创建水平埋氧化物,然后创建垂直氧化物沟槽,并将两者连接在一起以分隔n-well和p-substrate。氧化物沟槽是绝缘体,因此氧化物沟槽阻止了PNPN器件的形成。图13显示了氧化物沟槽隔离的横截面。

图13 沟槽隔离的横截面

4. 外延层:

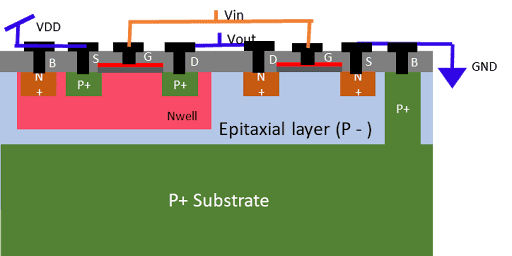

在这种技术中,低掺杂的p-外延层(称为P-)生长在P-substrate(称为P+)上。P-外延层为少数载流子提供低阻抗路径,可防止Latch-up触发。这种技术也称为P on P+。图14显示了CMOS使用外延层的横截面。

图14 使用外延层的CMOS的横截面

这项技术的唯一问题是,生长外延层是一个复杂的过程。另一种替代方法是可以使用外延晶片来实现这一目的。

5. 逆向井掺杂:

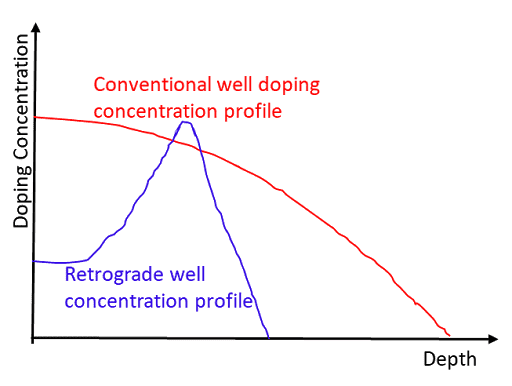

在正常的n-well掺杂过程中,掺杂浓度在表面最高,随着井深度的增加而降低。但是在逆向井掺杂过程中,对掺杂浓度在深度上有非常精确的控制,我们在n-well的深处有峰值掺杂浓度,而不是在表面。图15显示了正常掺杂和逆向井掺杂的掺杂剖面。

图15 逆梯度井掺杂的掺杂剖面

逆向井掺杂是在正常n-well底部进行的,如图16所示。该区域具有高掺杂浓度,并且创建了一个低电阻路径。取自N+掺杂的body连接延伸到这个高掺杂区域。因此,在n-well下方形成了一个低电阻路径,阻止了PNPN器件的触发。图16显示了逆向井掺杂的横截面。

图16 逆梯度井掺杂的CMOS

6. 外延层和逆向井掺杂的组合:

我们可以将外延层和逆向井掺杂两种技术结合使用,这也是一种非常有效的防止Latch-up问题的方法,但是该过程稍微复杂。

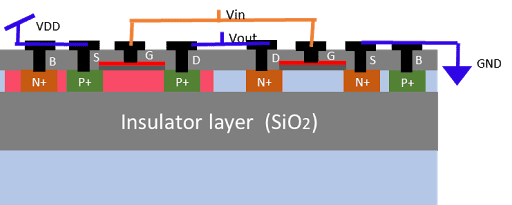

7. SOI技术:

在SOI(绝缘体硅)技术中,氧化物层位于源漏掺杂下方,并阻止寄生BJTs的形成。因此,SOI技术完全消除了Latch-up问题。图17显示了SOI技术中的CMOS的横截面。

图17 SOI技术中的CMOS

我们可以将外延层和逆向井掺杂两种技术结合使用,这也是一种非常有效的防止Latch-up问题的方法,但是该过程稍微复杂。

这些是在CMOS技术中防止Latch-up的方法。每种技术都有其优缺点。

需要注意的是:

- 闩锁不一定只发生在电源轨之间。只要寄生结构存在,就有可能发生门锁。

- 不止CMOS工艺会有Latch Up问题,bipolar也会有。只要有PNPN结构,就有可能门锁

更多井栓单元的知识,可以查看第5部分第3节。

[1] https://teamvlsi.com/2020/05/latch-up-is-in-cmos-design.html

[2] https://teamvlsi.com/2020/05/latch-up-prevention-in-cmos-design.html