4.2 IR压降分析

在本文中,我们将讨论 ASIC 设计中 IR 压降是什么,为什么会出现 IR 压降问题,IR 压降的影响是什么,以及如何分析和预防 IR 压降问题。

IR 压降问题是什么:

IR中的 I 是指电流,R 是指电阻,他们相乘就是电压。故 IR drop 就是电压降。

通俗来讲,电压降,就是指从芯片源头供电到instance所消耗的电压,对于flipchip封装形式,就是从bump到instance PG pin的电压降。Instance实际得到的电压就是供电电压减去电压降的部分。比如bump接的外界输入电压Vdd 5V,Vss 0V,这个bump的电压到某一个instance后,可能Vdd只剩4V,Vss变为1V,那么这个instance得到的电压就只有3V,电压降就是2V。IR drop是芯片后端signoff的一项重要内容,必须保证IR drop不能过大,否则芯片可能会因为得不到所需的电压而发生逻辑错误或停止工作。这个IR drop也是会有相应spec要求的,一般会按照供电电压的百分比来定,如果定了10%,对于5V的输入来说,就要求IR drop不能大于0.5V。

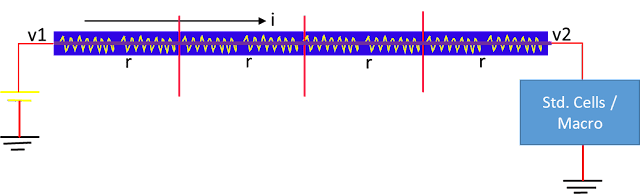

理论来讲,芯片中的电源(VDD 和VSS)通过金属导轨和条纹均匀分布,这被称为电源传输网络(PDN)或电源网格。PDN 中使用的每个金属层具有有限的电阻率。当电流通过电源传输网络时,根据欧姆定律,应用电压的一部分将在 PDN 中降低。图1显示了电源网络中的 IR 压降。任何金属网都可以假设为小 R 和 C 的组合。

图1 金属网中的 IR 压降

如果金属导线的电阻率较高或通过电源网络的电流量较大,则电源传输网络中可能会降低大量电压,导致标准单元可用电压少于实际应用电压量。如果在电源端口施加 V1 电压,并且在具有总电阻 R 的特定网中流动电流 I,则标准单元的另一端可用电压(V2)将为

由于电源传输网络中的 IR 压降,有时标准单元或宏单元无法获得所需的最小工作电压来使其运行,即使在电源端口施加足够的电压。在到达标准单元之前电源传输网络中的电压降称为 IR 压降。

这种降低可能导致芯片性能不佳,因为标准单元的延迟增加,可能导致芯片功能故障,从而产生建立/保持时间违规。为避免此问题,必须进行 IR 分析,并在设计周期中考虑其在时序分析中的影响。

IR 压降的类型

ASIC 设计中有两种类型的 IR 压降:

- 静态 IR 压降

- 动态 IR 压降

静态 IR 压降

静态 IR 压降是指当没有输入切换时(即电路处于静态阶段)电源传输网络(PDN)中的电压降。静态IR drop现象产生的原因主要是电源网络的金属连线的分压,是由于金属连线的自身电阻分压造成的。所以静态IR drop主要跟电源网络的结构和连线细节有关。 因此静态IR drop主要考虑电阻效应,分析电阻的影响即可。静态压降的计算不考虑电流随时间的变化,或者说以很长一段时间内的平均电流代指instance的电流。

R值的计算也相对简单,不会过多考虑电流趋肤效应对电阻的影响,主要考虑电源网络的结构和连线细节。可以由PG网络抽取出R值,并认为它也是恒定不变的。

这样,IR相乘得出静态压降也是一个不变量,算静态压降的意义在于可以快速评估芯片的PG网络如何,powerplan是否做的足够好。如果出现许多static IR的violation,可能就需要重新调整PG网络。那么,static IR的这个平均电流是如何得到的呢?实际上,我们是先利用primepower等算power的工具先算出instance的power值,再根据power和instance的电阻得出流过他的电流。

动态 IR 压降

而动态 IR 压降是指当输入连续切换时(即电路处于功能状态)电流波动引起的电源传输网络中的电压降。动态IR drop是电源在电路开关切换的时候电流波动引起的电压压降。这种现象产生在时钟的触发沿,时钟沿跳变不仅带来自身的大量晶体管开关,同时带来组合逻辑电路的跳变,往往在短时间内在整个芯片上产生很大的电流,这个瞬间的大电流引起了IR drop现象。同时开关的晶体管数量越多,越容易触发动态IR drop现象。

动态 IR 压降取决于实例的切换速率。 Dynamic IR的计算相对复杂,它考虑了电流随时间的变化,通过对芯片长时间的模拟,可以认为某个instance的电流是随时间周期性变化的,相应的它的IR drop也会是一个随时间变化的函数。

一般会有三个比较关心的指标:peak IR、average IR、RMS IR。Peak IR即为电压降的峰值,我们需要保证峰值压降也在可接受范围内。Average IR指的是每个周期的平均压降,其实也有点类似static IR,但是计算方式会有所差异。RMS IR指root mean squre IR,也就是算IR drop随时间变化的方差,有的时候我们需要保证instance的电压降要平缓的变化,RMS就可以反映电压降随时间的离散程度。一般来说,dynamic IR的计算耗时很长,适用于找到个别instance的violation,而后针对性的调整某个instance。可以挪动它的位置到IR比较好的区域,也可以针对性的在某一块补一些PG mesh。

当输入连续切换时,实例中会流动更多的电流,同时也会在PDN中流动更多的电流。因此,在PDN中会有更多的 IR 压降。因此,动态 IR 压降大于静态 IR 压降。

IR 压降的原因

IR 压降可能由于各种原因而发生,但主要原因有以下一些。

- 电源传输网络设计不佳(金属宽度较小,电源条纹之间间距较大)

- 电源传输网络中适当数量的过孔不足

- 解耦电容单元(DeCap Cell)的数量不足

- 特定区域中高细胞密度和高开关

- 电源传输网络的高阻抗

- 突发电流

- 电压源数量不足

- 用于创建电源传输网络的金属层的高 RC 值

IR 压降的影响

标准单元的延迟取决于单元的可用电源,如果电源供应减少,则单元的延迟增加。 单元延迟的增加可能影响设计的性能。如果标准单元的可用电压降至特定水平以下,则单元可能完全停止运行,导致设计的功能故障。 或者有时,IR 压降在限制范围内只会增加单元的延迟,从而影响设计的建立和保持时间,并有时导致建立时间(setup time)和保持时间(hold time)违例。setup的违例,可以通过抬高电压来提升频率,但是代价是功耗上去了,而且如果动态IR drop不够robust,可能通过抬电压,setup能提升的空间也有限。而一旦出现hold违例,那芯片就无法正常工作。因此在先进工艺中,IR drop的影响特别大,需要引起各位的高度重视。

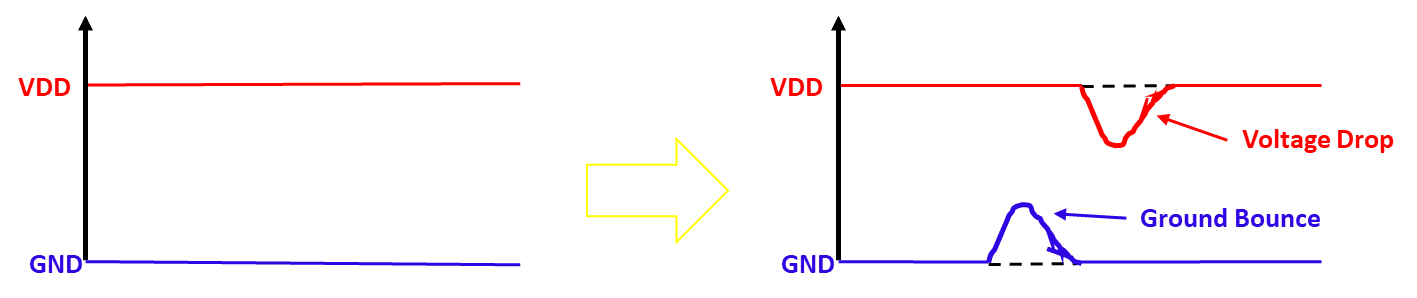

如果由于某个特定区域的大量开关活动,导致当前需求突然增加,VDD 线路也可能会突然下降。此类 VDD 水平下降称为电压下降。或可能会导致地线电压水平突然升高,称为地弹跳。这些统称为电源噪声。 图2 显示了由于 IR 压降导致的电源噪声。

图2 由于 IR 压降导致的电源噪声

简而言之,IR 压降可能导致:

- 单元延迟的变化

- 可能违反建立和保持时间

- 引入电源噪声到电源网络

IR 分析和修复:

每家 EDA 公司都有自己的 IR 分析工具,该工具执行 IR 分析,并基于分析应用 IR 修复技术。工业中使用的两种最流行的 IR 分析工具是:

- Ansys 的 RedHawk

- Cadence Design System 的 Voltus

根据分析,会应用各种修复 IR 压降的技术。通常执行的一些修复措施包括:

- 插入足够数量的解耦电容单元(DeCap Cell),以增强电源传输网络。

- 如果电源传输网络构建不正确,重新构建电源传输网络。我们可以增加金属条纹的宽度或减小它们之间的间距。

- 我们可以在一个区域内扩展逻辑单元,以便负载可以分布。

更多解耦电容单元的知识,可以查看第5部分第4节。

谢谢

[1] https://teamvlsi.com/2020/07/ir-analysis-in-asic-design-effects-and.html

[2] https://zhuanlan.zhihu.com/p/450521738

[3] https://zhuanlan.zhihu.com/p/544002432