4.7 理解和应对OCV

在物理设计中,OCV是指芯片内部电路实际性能与标准预期性能之间的差异。简单来说,OCV描述了芯片内不同区域之间的电性能变化情况。这种变化可能是由于制造过程中的不完美或环境条件的波动引起的。

在本文中,我们将讨论VLSI中 OCV [On-Chip Variation:芯片内变异] 的来源,为什么会发生芯片内变异以及如何在物理设计中处理芯片内变异。我们还将简要讨论 AOCV [Advance On Chip Variation:高级芯片内变异] 和 POCV [Parametric On Chip Variation:参数化芯片内变异]。

背景:

在ASIC设计周期中,在物理设计和签署之后发送到制造实验室的最终输出是.gds(图形设计系统)文件。IC(集成电路)是基于这个最终的gds数据在硅晶圆上制造的。一个大的硅晶圆被分成各种小芯片,每个芯片包含一个独立的IC。在晶片级测试之后,我们切割和分离每个芯片,对IC进行封装。

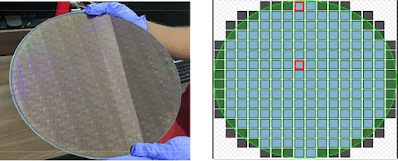

所有芯片中的所有IC都具有相同的gds数据,但芯片在晶圆上的位置不同。如果所有芯片的gds都相同,那么理想情况下所有IC的电特性应该相同。但实际上并非如此。在不同芯片中制造的IC的电特性会有所不同。图1显示了硅晶圆和晶圆上的芯片。

图1 硅晶片和晶片载体上的芯片

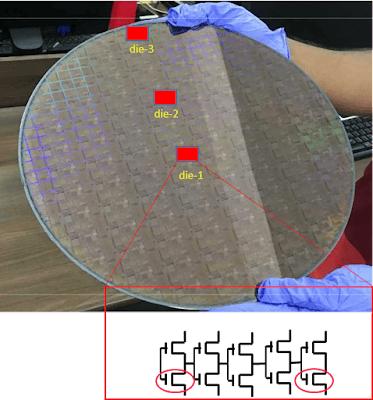

例如,让我们考虑图2中显示的位于晶圆不同位置的三个芯片。芯片1位于晶圆中心,芯片3位于晶圆边缘,芯片2位于中心和外缘之间。

图2 晶片、芯片和芯片内的晶体管

因此,在一个晶圆内有成百上千个芯片,并且每个芯片中都存在变异,同时在许多晶圆中也存在变异。或者如果我们深入调查,我们会发现IC内部有数百万个晶体管,单个IC内的所有晶体管都不相似。因此,即使在单个IC内部以及在芯片和晶圆中,晶体管的特性也会存在变异。现在一个重要的问题出现了,所有这些变异是从哪里来的?这些变异的根本原因是什么?答案是制造过程本身是这些变异的主要原因。所以让我们调查这些变异的来源。

变异源:

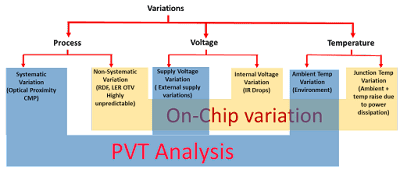

变异有三个主要来源,即工艺、电压和温度。这些变异统称为PVT变异。我们已经在设计ASIC时进行了PVT分析并处理了这些变异,那么为什么我们需要单独处理OCV呢?答案是,并非所有变异都可以在PVT分析中处理。其中一些是可预测的,并且随着技术的成熟可以轻松建模,但其中一些是非常不可预测的,无法轻松建模。图3显示了PVT和OCV变异的各个组成部分。

图3 PVT和OCV下的变化元件

工艺变异中有两种类型的变异,一种是系统变异,另一种是非系统变异或随机变异。系统变异是由光学近邻修正(OPC)或化学机械抛光(CMP)引起的,这些变异是可预测的,并且可以在PVT变异中建模。非系统变异来自随机杂质波动(RDF)、线边粗糙度(LER)或由于氧化物厚度变化(OTV)引起的变异,这些变异是非常不可预测的,无法轻松建模。或者我们可以说这些变异是随机的。

在电压变异中,一种是由外部供电电压变异引起的,另一种是芯片内部电压变异。没有理想的电压供应,即使在供电电压设计中采取了最大的注意,供电电压仍然会有2-5%的变异。这种类型的变异在PVT中得到处理,但另一种类型的变异是由于内部IR降,这种变异不可能在PVT中建模,因为它是随机的,并且取决于设计。因此,我们需要在OCV中处理这种电压变异。

如果谈论温度,那么芯片运行的环境温度和晶体管的结温是关键。结温是环境温度加上由芯片功耗引起的温升的总和。结温始终远高于环境温度,任何晶体管的特性主要取决于结温。环境温度可以在PVT中处理,但对于结温变异,我们需要在OCV中处理。

让我们进一步讨论所有这些变异。

I. 工艺变异:

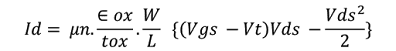

线性区域中nMOS晶体管的漏极电流可以定义为

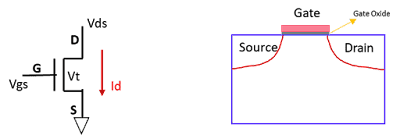

其中Id为漏极电流,μn为电子迁移率,∈ox为硅氧化物介电常数,tox为氧化物厚度,W为晶体管的宽度,L为晶体管的栅长,如图4所示。

图4 MOS器件的引脚和原理图

在漏极电流方程中,依赖于制造工艺的因素包括:

- 栅氧化物厚度(tox)

- 晶体管的宽度(W)

- 晶体管的长度(L)

- 晶体管的阈值电压

因此,如果上述因素中的任何一个在制造过程中发生变化,它都会影响漏极电流。电池的延迟取决于漏极电流,因此由于工艺变异,标准电池的延迟将会变化。现在看一些示例,这些参数在制造过程中如何受到影响。图5和图6显示了与光刻工艺相关的长度和宽度变异。

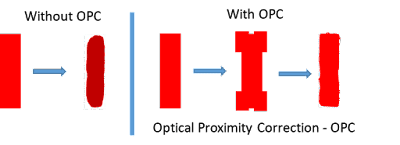

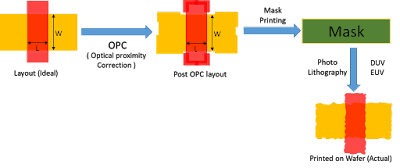

图5 光刻近邻修正

光刻工艺是应用于掩膜生成之前的布局的一种过程,以便在晶圆上更好地复制布局。在此过程中,通常将布局的角落边缘延伸以获得更好的产量。图6显示了一般的光刻工艺流程。

图6 光刻工艺流程

光刻工艺是一个非理想的过程,很难在硅晶圆上准确印刷出精确的布局。因此,实际布局和在晶圆上印刷的几何形状之间存在变异。

以下是一些常见的工艺变异类型及其含义:

光刻工艺:光刻是一种制造芯片中非常重要的工艺步骤。它使用光刻胶和掩模模板来定义芯片上的图案和结构。光刻工艺的变异可能导致掩膜对光刻胶的曝光不均匀或模糊,进而影响芯片上的结构精确性和尺寸精度。

光学近邻修正(OPC):OPC是一种在光刻过程中使用的技术,通过微调掩模图案的形状和尺寸,以消除由于光学效应而引起的图案畸变。然而,OPC本身也可能引入变异,如在边缘处形成额外的形态、尺寸变化或形状失真。

随机杂质波动(RDF):RDF是由芯片制造过程中的随机杂质或不完美引起的,如掺杂杂质、尘埃颗粒等。这些随机杂质可能会在芯片内部或表面引起电场或电流的变化,从而对电路性能产生不可预测的影响。

线边粗糙度(LER):LER描述了制造芯片时金属线路边缘的不规则程度和表面粗糙度。这种不规则程度可能会导致电流分布不均匀,产生电阻、电容等电路性能的变化。

蚀刻:蚀刻是一种用于去除芯片表面或层之间多余材料的工艺过程。蚀刻过程中的变异可能导致不均匀的材料去除,进而引起结构的形状、尺寸或结构剖面的变化。

化学机械抛光(CMP):CMP用于平整化芯片表面,以去除蚀刻之后产生的凸起或不平整表面。然而,CMP过程中的变异可能导致材料厚度的不均匀去除,进而影响芯片上结构的形状和尺寸。

氧化物厚度变化(OTV):在芯片制造过程中,氧化物常用于隔离和绝缘材料。然而,由于制造过程中环境条件的波动,氧化物的厚度可能会出现变异,从而影响芯片上的电介质特性和电场分布。

因此,总之,在芯片制造过程中存在许多因素和高概率的变异,这可能导致标准电池的延迟变化。

II. 电压变异:

外部电压变异在PVT中得到处理,但是基于设计,芯片内部可能发生电压变异。您的功率传递网络中可能会发生IR下降,这可能导致操作单元的可用电压发生变化。

电源来自电源垫/凸点,并通过金属条和轨道分配给芯片内部所有标准单元,这被称为电源传递网络(PDN)或电源格。电源垫和标准单元之间的距离可能对所有标准单元都不相同。因此,标准单元的可用VDD会根据设计而有所不同。单元的延迟取决于可用的VDD,如果VDD较低,则延迟会更大。

III. 温度变异:

晶体管的特性严重依赖于结温。根据ASIC的应用,环境温度在PVT中得到处理。但是结温取决于芯片的设计。芯片内部的功耗会提高附近结温的温度,并可能影响整个芯片的性能。

有时,根据单元的放置密度和功率需求,还会形成局部热点,这会影响结温,最终导致单元的电流和延迟变异。结温是环境温度和由单元功耗引起的温度之和。这整个过程是不可预测的,无法在PVT中处理,因此我们必须在OCV中处理这些变异。

芯片内变异的影响:

如果在设计ASIC时不处理芯片内变异,可能会导致后硅失败。考虑这样一种情况,由于OCV,数据路径中的延迟增加或启动时钟路径中的延迟增加,或者捕获时钟路径中的延迟减少。在所有情况下,由于OCV可能导致建立时间违规。保持时间也可能出现类似情况。如果不处理OCV,一个正确的时序闭合芯片可能会违反时序并失败。

如何处理OCV:

为了处理OCV,我们需要在标准单元的时序中添加一些悲观主义。我们基本上对所有标准单元应用±x%的额外延迟。这被称为OCV降级。

OCV降级系数:

降级系数是处理芯片内变异的一种非常简单的方法。在整个设计中应用一个固定的降级系数。这样,在发生任何变异的情况下,不会导致芯片的失败。但它添加了太多的时序悲观主义,导致在时序闭合方面出现困难,特别是在较低节点中。

因此,该行业已经从固定降级转向基于距离和深度的降级,这被称为高级芯片内变异(AOCV)。随着技术节点的进一步缩小,AOCV也不是一个很好的选择,进一步发展了参数化芯片内变异(POCV)。我们将在另一篇文章中讨论OCV、AOCV和POCV。简而言之,我们可以说随着我们从OCV进展到POCV,时序悲观主义减少了。

[1] https://teamvlsi.com/2020/07/on-chip-variation-in-vlsi-ocv-in-physical-design.html