4.5 信号完整性与串扰效应

根据Collett International Research Inc.的研究显示,约五分之一的芯片因为信号完整性问题而失败,这个数据可不是闹着玩的!这就让我们不得不深入探讨VLSI设计中一个极其重要的话题——信号完整性和串扰。

信号完整性:

首先,让我们先来理清一下什么是信号完整性。信号本质上是以波/脉冲形式传输的信息,用于实现不同点之间的通信。比如,数字形式中的信号可以是状态1(高电平)或状态0(低电平),就像二元世界里的语言。如下图所示。

图1 数字信号

根据定义,完整性意味着“完整或未受损”。或者我们可以说,在不失真的情况下,随着时间的推移保持任何事物的实际形式。因此,信号完整性可以定义为在从一个点传输到另一个点时,信号的整体复制而没有任何质量上的失真。或从更广泛的角度来看,我们可以说信号完整性是电信号可靠携带信息并抵抗来自附近信号的高频电磁干扰的能力。

在信号完整性这个话题中,我们会碰到三大要素:信号、芯片、传输通道。信号就是被传输的主体,了解信号的特性是首要任务;而芯片分为驱动芯片和接收芯片,信号完整性工程师需要确保信号能够在这两者之间正确传输;传输通道则是信号所走的“路”,需要信号完整性工程师来“修路”、“搭桥”,确保信号畅通无阻。

- 信号:是被传输的主体,我们首先要了解、熟悉信号的特性。

- 芯片:分为驱动芯片和接收芯片,信号完整性工程师就是要实现信号在驱动芯片和接收芯片之间的正确传输。

- 传输通道:是传输信号的介质,是信号所走的“路”。如何实现信号的正确传输呢?那就要信号完整性工程师为信号“修路”、“搭桥”。

信号完整性解决数字设计中的两个问题:

- 信号的时序 - 信号是否在预定时间到达目的地?

- 信号的质量 - 信号到达时,质量是否良好?

在高速数字设计中,“时序”非常重要。

因此,信号完整性的目标是确保可靠的高速数据传输从芯片内的一点到另一点通过金属线路。随着数据速率的提高和技术节点的降低,保持信号完整性是一个巨大的挑战。简而言之,如果信号在网络中传输时没有任何失真,信号完整性就很高;如果有许多噪声添加/失真发生/延迟发生,信号完整性就较低。

除了以上提及的关键问题,信号完整性往往还受到各种其他因素的影响。串扰(Crosstalk)便是其中之一,当不同信号之间相互干扰时,可能导致信号失真和延迟。此外,地弹跳(Ground Bounce)也是一个常见问题,大量电流在地线上产生变化时可能导致地电位波动,从而影响信号传输。还有IR降压、天线效应、电迁移等等。

什么是串扰?

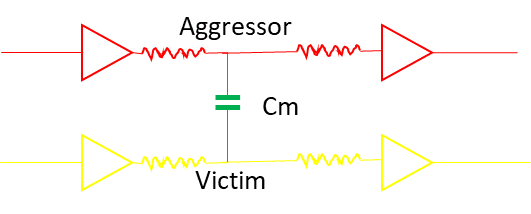

串扰可以定义为一个现象,在其中一个网络中传输的逻辑对其相邻网络产生了不希望的影响。 换句话说,一个网络中信号的切换可能会干扰相邻网络,这就是串扰。当一个信号切换时,它可能会影响相邻网络的电压波形。切换网络通常被称为“侵略者”,受影响的网络被称为“受害者”。图2显示了典型的侵略者和受害者网络的排列方式。

图2 侵略者和受害者网络

串扰是一种非常严重的影响,特别是在较低技术节点和高速电路中,它可能是芯片故障的主要原因之一。在下一节中,我们将讨论VLSI设计中的串扰机制。

串扰机制

串扰通过两种机制发生:

- 感应串扰

- 静电串扰

感应串扰是由于两个网络之间的互感现象而发生的。一个网络中的变化电流会在网络周围产生变化的磁场。变化的磁场既可以通过发射无线电频率波来辐射能量,也可以与相邻网络耦合。这种磁场的耦合称为感应串扰。

静电串扰是由于两个网络之间的互电容而发生的。一个网络中的电压会在其周围产生电场。如果电场发生变化,它既可以通过辐射无线电波,也可以以电容方式与相邻网络耦合。这种电场的耦合称为静电串扰。

在这里解释的两种机制中,静电串扰机制比感应串扰更显著和有问题。

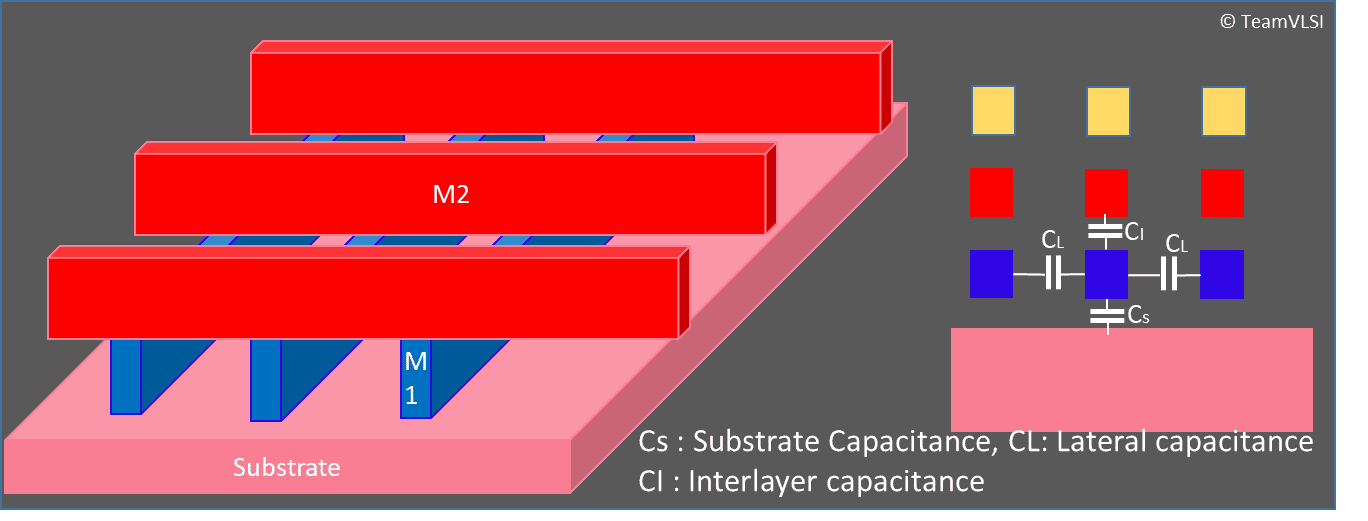

与互连相关的寄生电容

串扰的主要原因是互连之间的电容。因此,在本节中,我们将调查与金属互连相关的各种电容。图3显示了ASIC内部形成的各种寄生电容(点击图像以查看更好视图)。

图3 与互连相关的各种电容

在FEOL(前端线)制造完成后,在金属-1(M1)层制造之前,在整个基片上沉积了一层厚的SiO2绝缘层。M1和基片之间的绝缘层充当介质,并形成M1和基片之间的电容,这称为基片电容(cs)。 M1被加工,并且不需要的金属区域被蚀刻掉,然后再用SiO2填充空区域。因此,在两个相邻的M1网(相同的金属层)之间形成了寄生电容,称为侧向电容(CL)。在M1上方制造M2层,然后是SiO2层。因此,在任何两个相邻金属层之间形成了互层电容(CI)。互层电容不仅可以形成互连金属之间,还可以形成相距较远的金属之间,例如M2-M4或M2-M5。所有这些电容的值取决于两个因素:公共面积和它们之间的间隙。这些电容与它们之间的公共面积成正比,与它们之间的间隙成反比。

谢谢

[1] https://teamvlsi.com/2020/06/signal-integrity-and-crosstalk-in-vlsi.html

[2] https://blog.csdn.net/qq_29476769/article/details/122854047

[3] https://blog.csdn.net/qq_29476769/article/details/122933743

[4] https://blog.csdn.net/qq_29476769/article/details/122953752